preamble

This article installs Gowin, Gowin’s development software, and describes the development environment and complete download and runtime of a program based on Gowin’s fpga.

Gowin Software

summarize

Gowin software is the FPGA development software of Guangdong Gowin Semiconductor Co.

download address

http://www.gowinsemi.com.cn

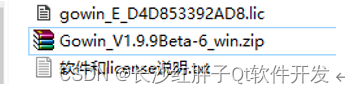

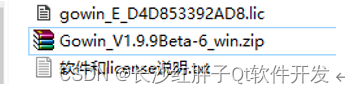

Apply for license

Apply for license at http://www.gowinsemi.com.cn/faq_view.aspx

There is also a harmonious way this process can be viewed:

http://www.corecourse.cn/forum.php?mod=viewthread&tid=29510

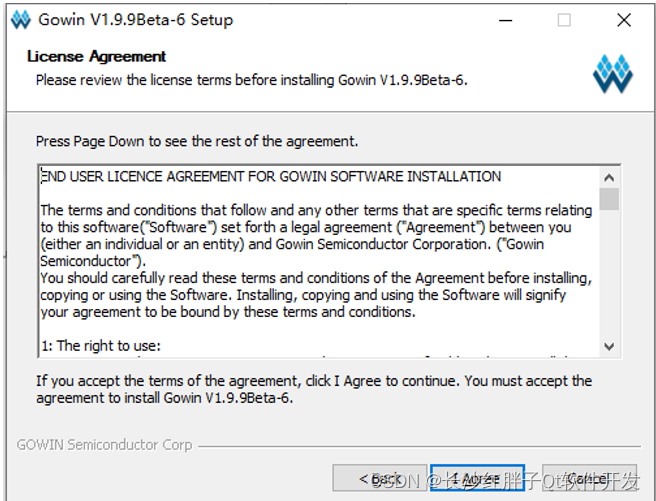

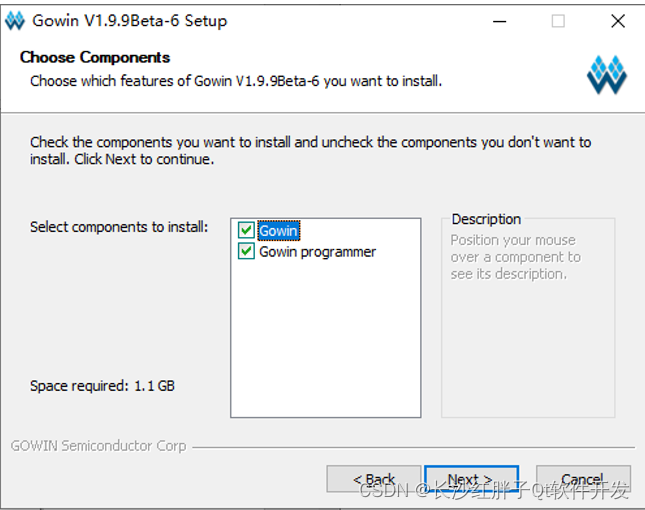

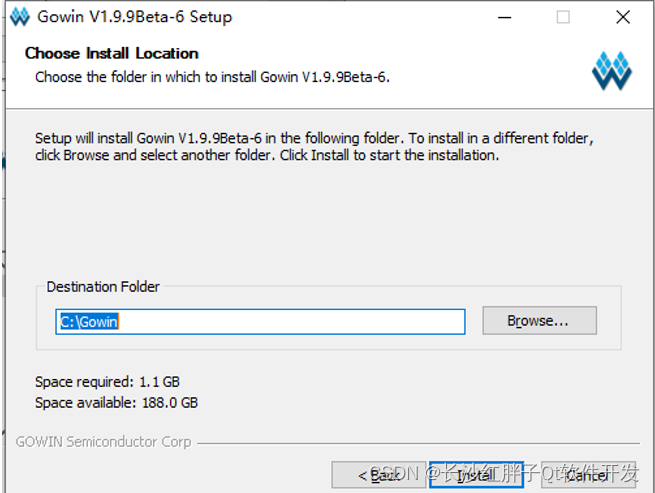

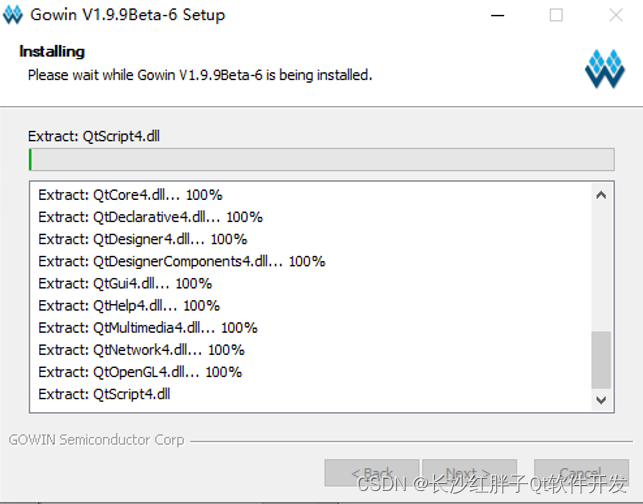

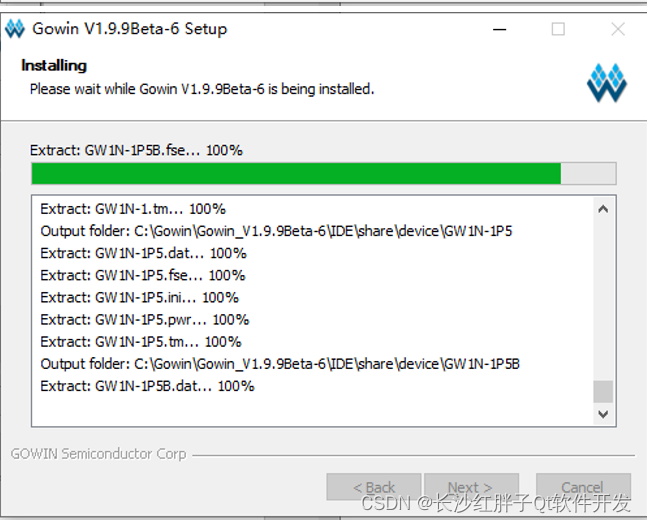

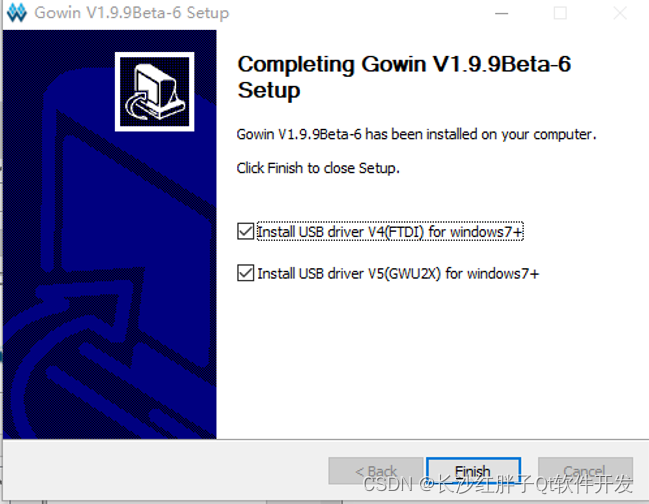

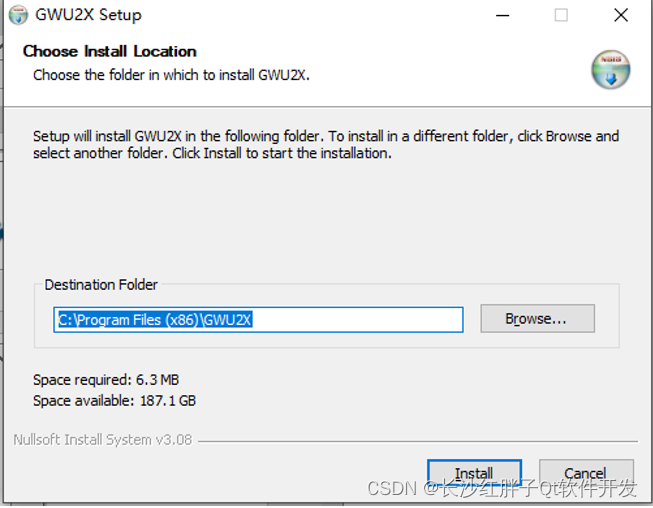

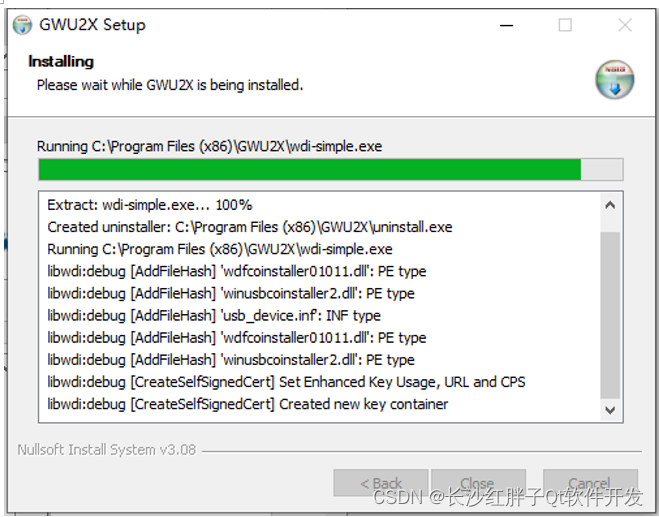

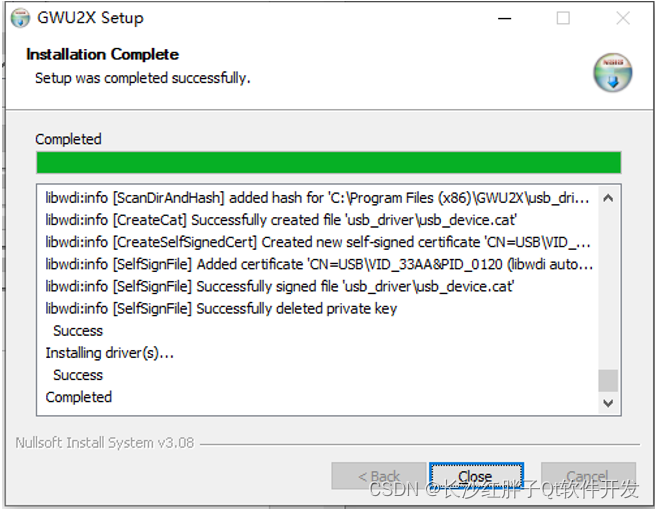

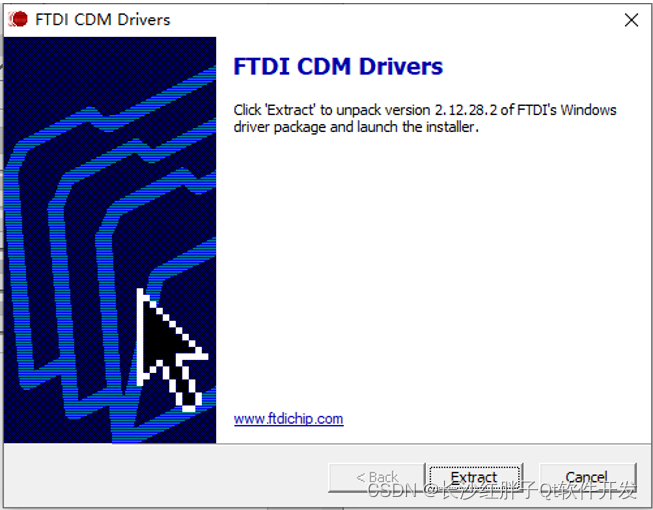

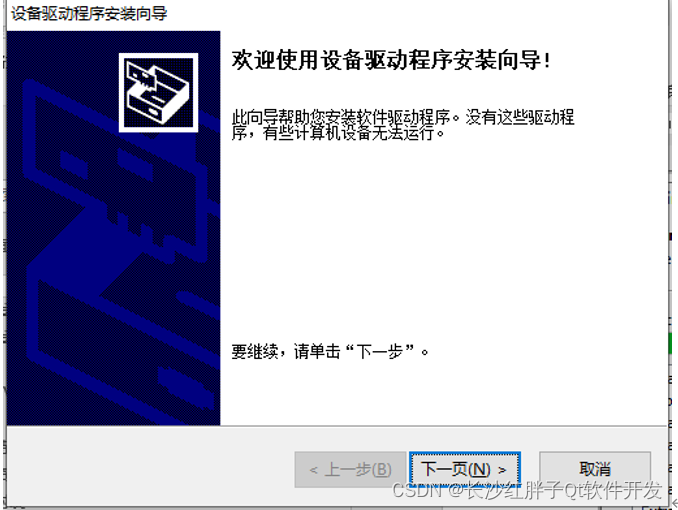

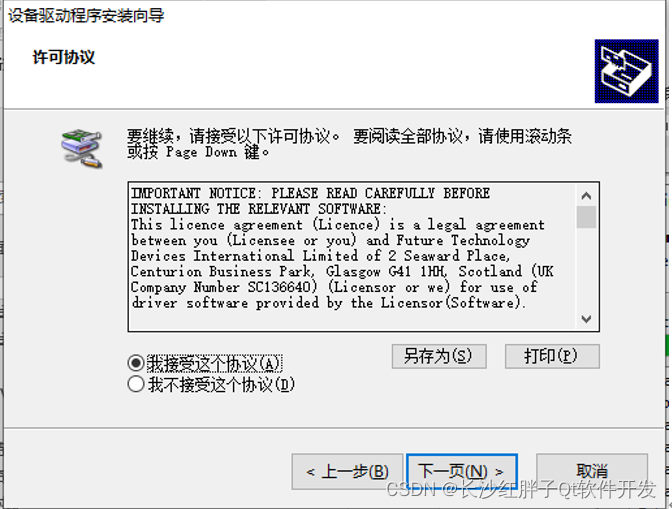

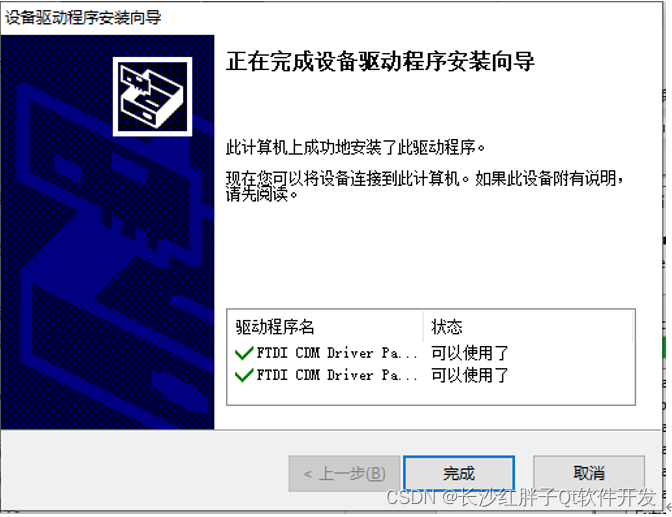

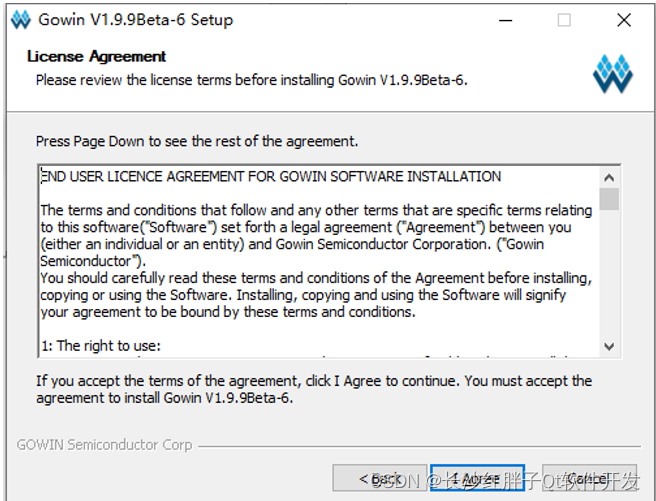

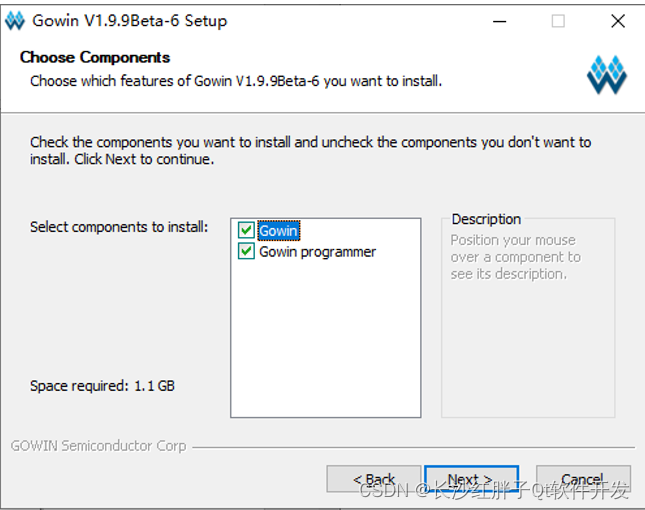

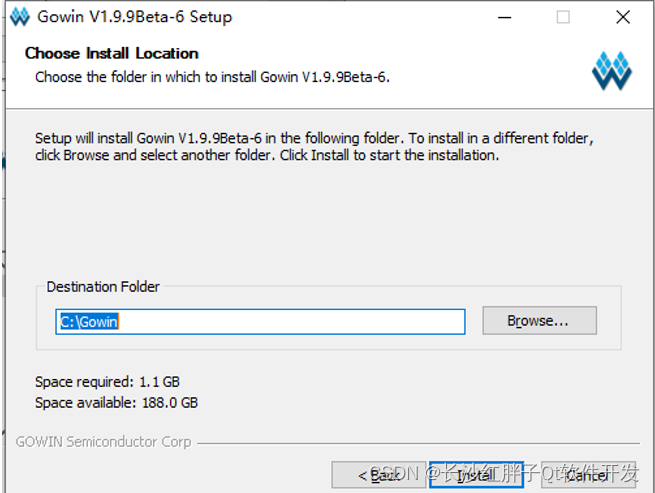

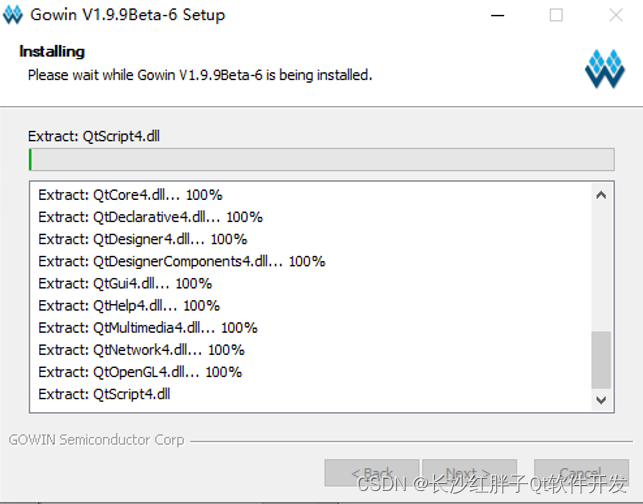

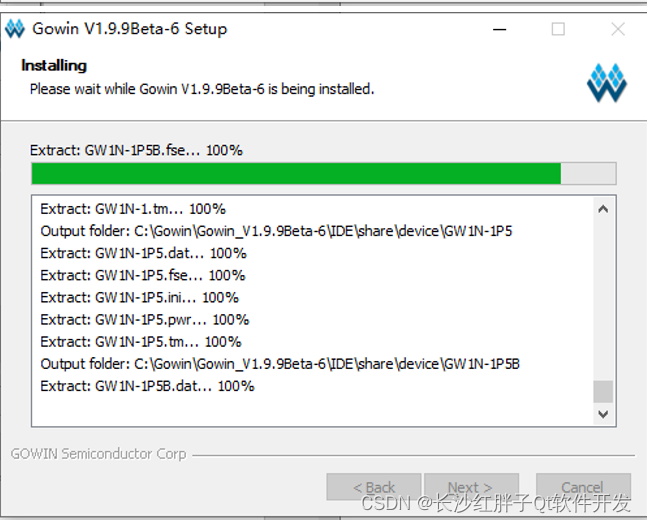

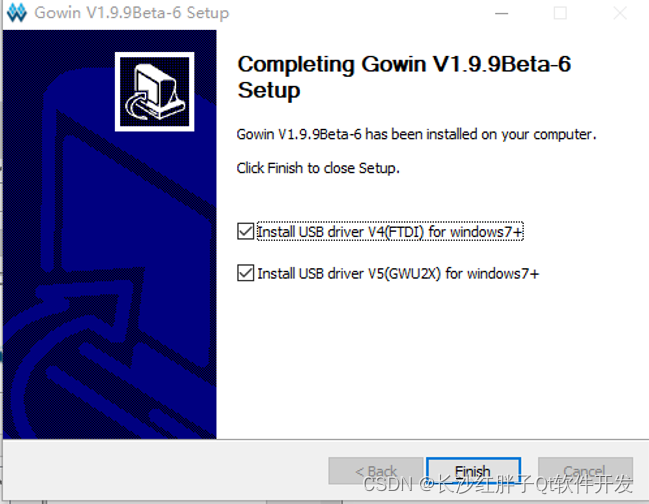

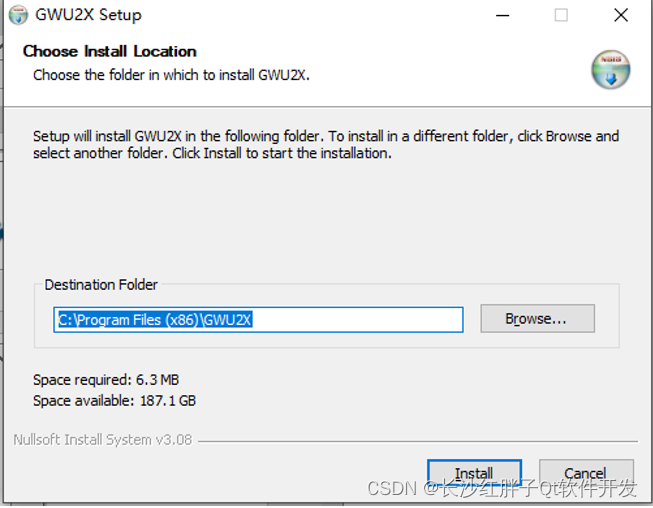

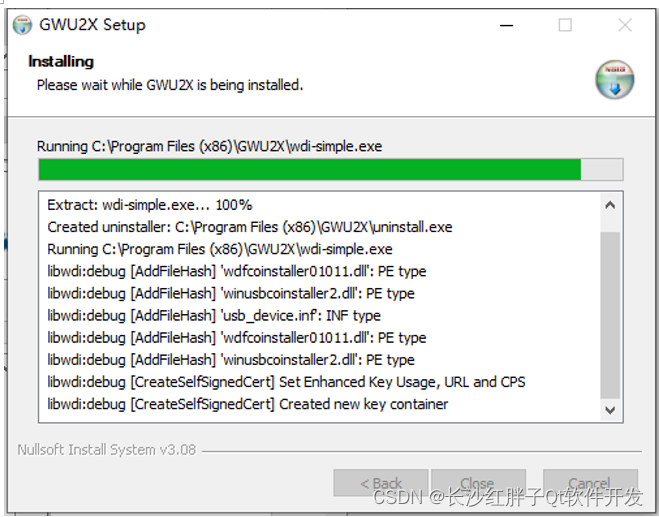

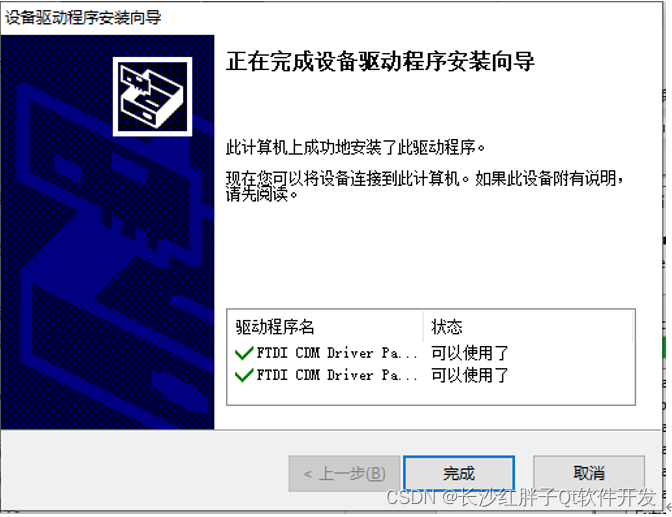

After downloading the software and getting the license it is time to install the software.

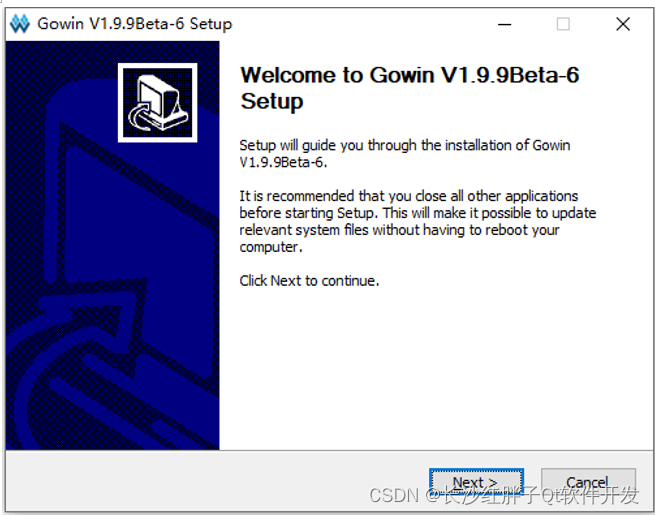

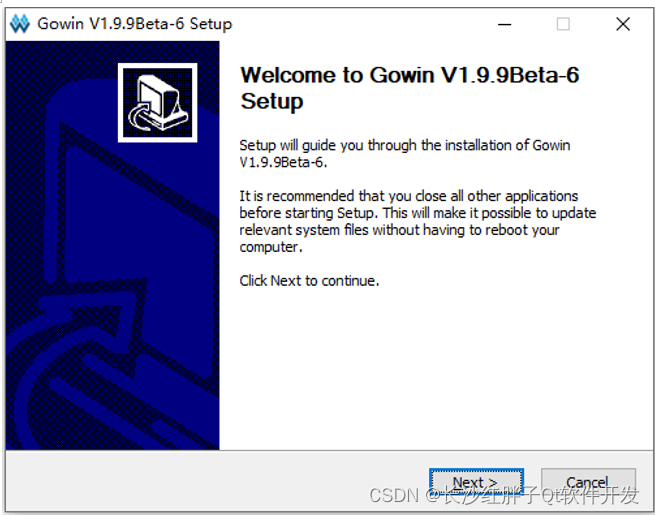

Installation of Gowin Software

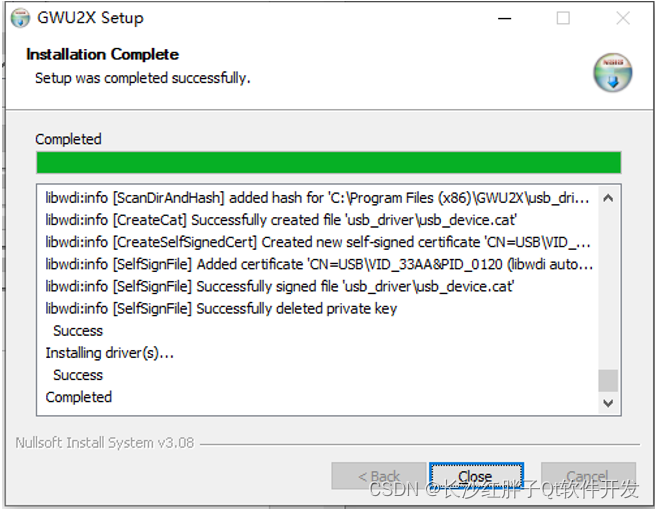

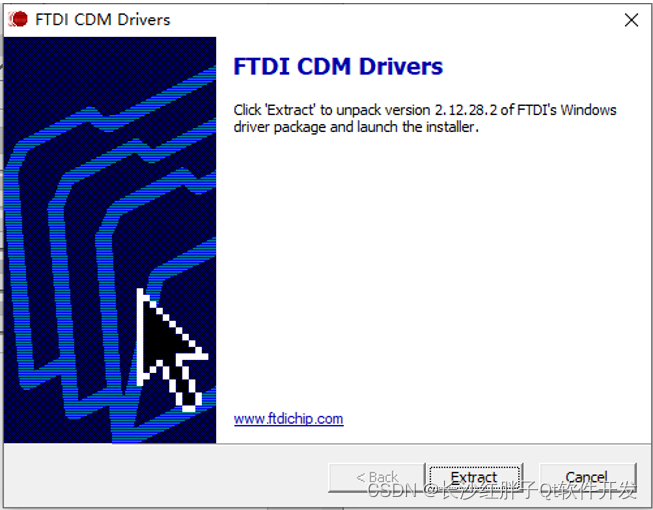

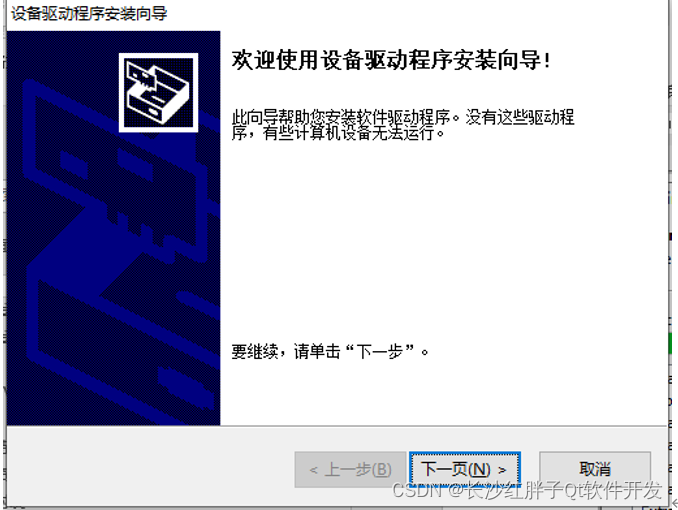

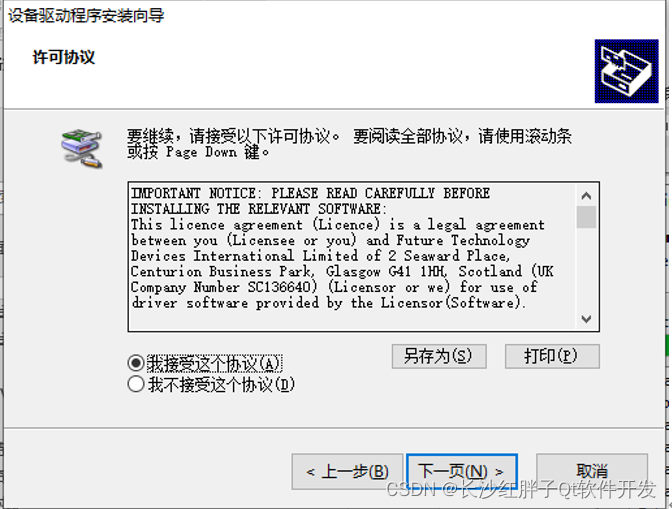

Then, there was no more then, it was straight up gone, it was the installation that was done.

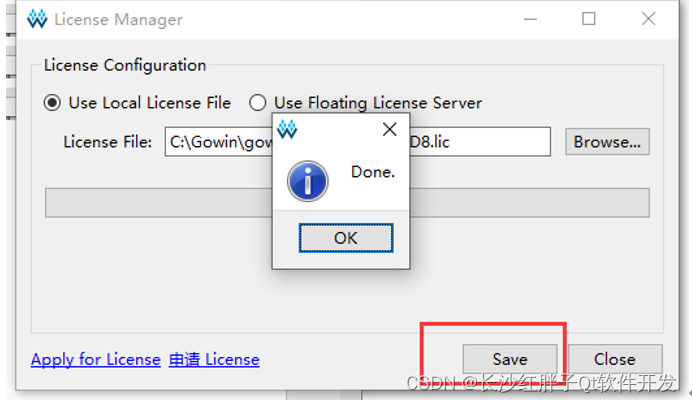

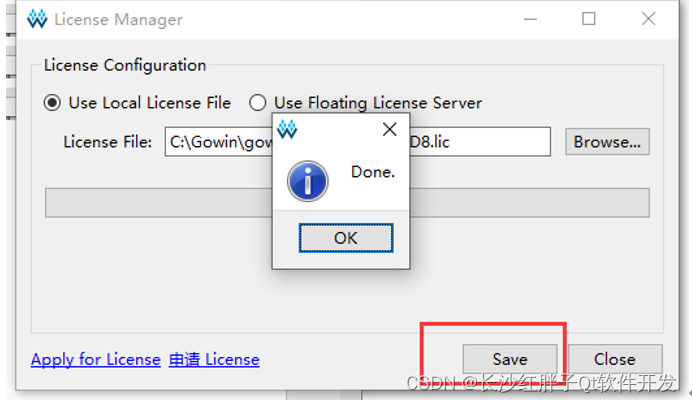

License Registration

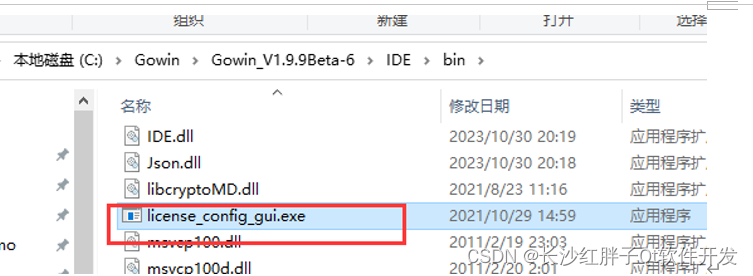

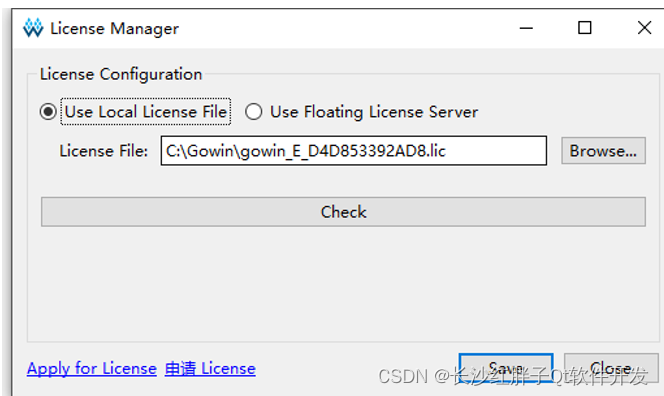

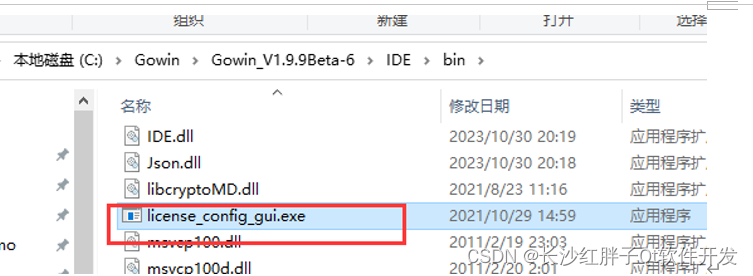

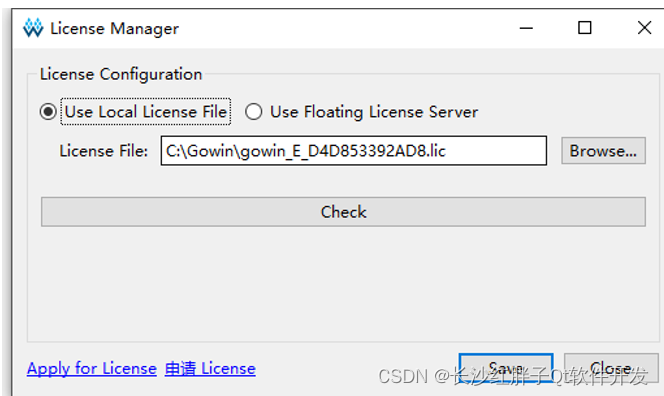

This is no license, open the installation directory:

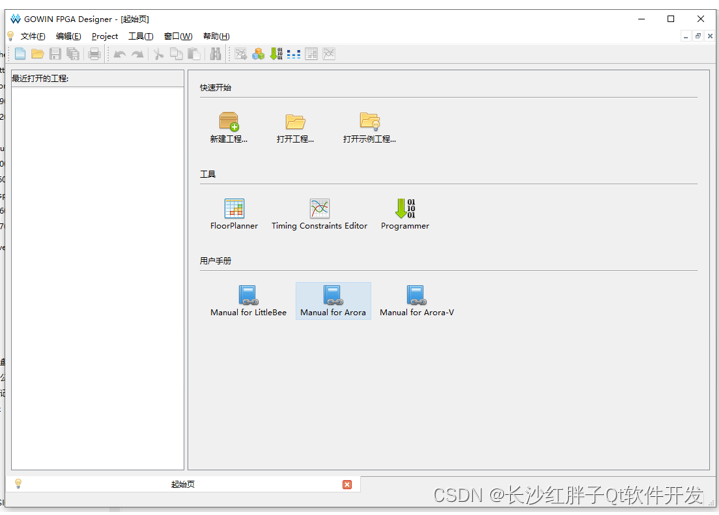

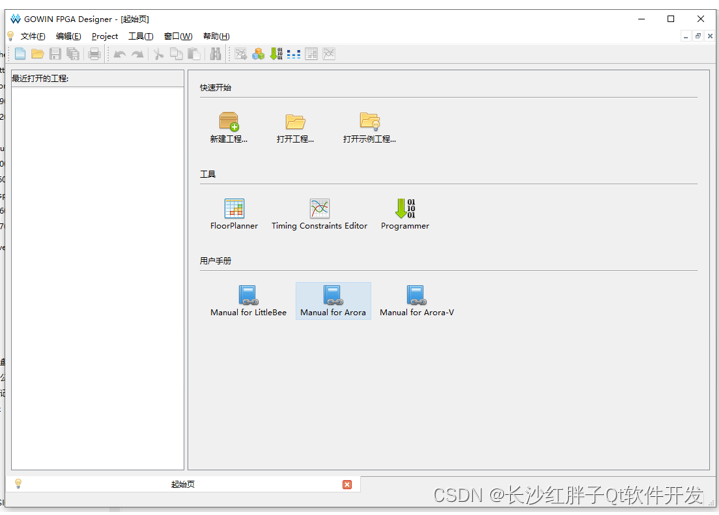

boot software

Drag it out and place it on the Start screen:

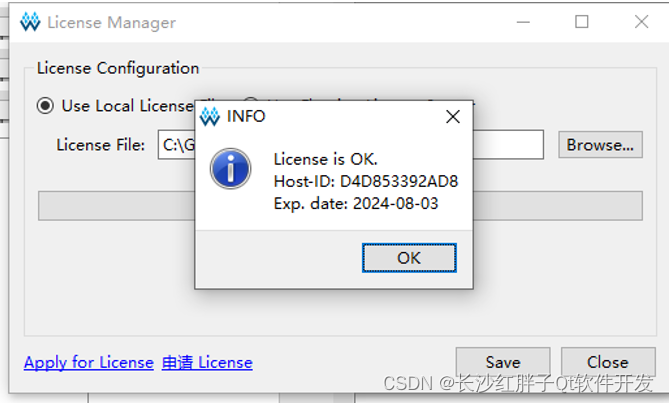

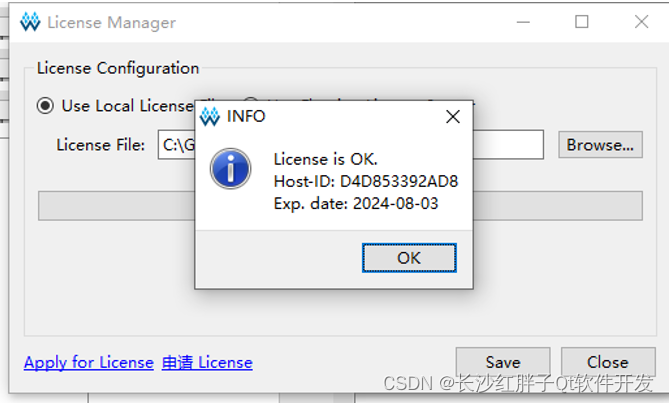

Click to open:

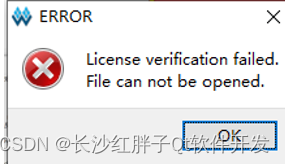

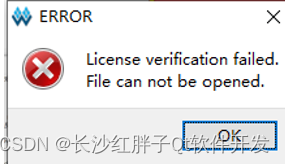

Above is the registration license failed or unregistered, go back and continue to register.

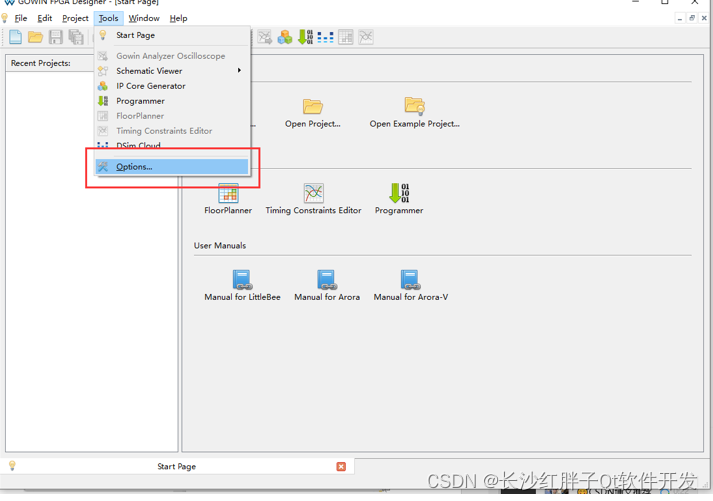

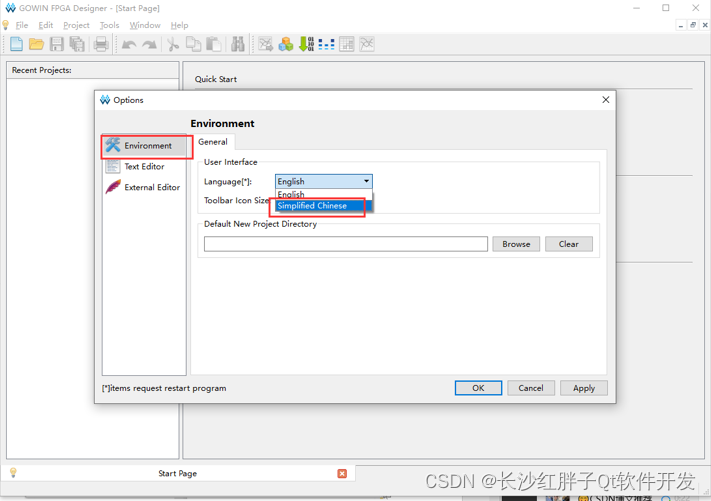

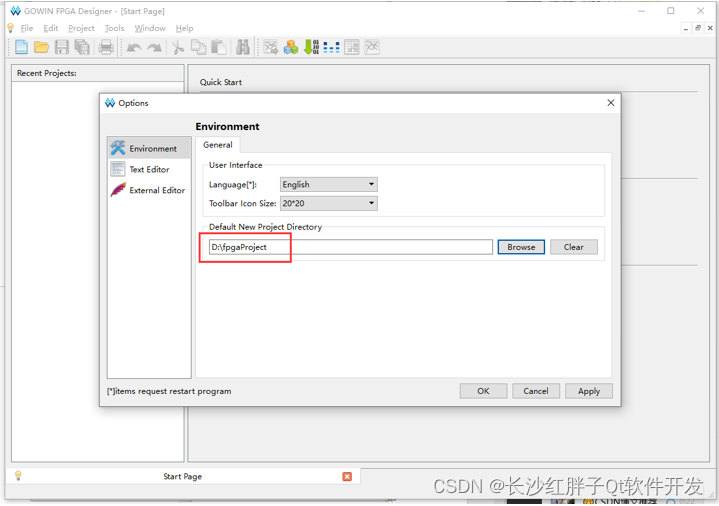

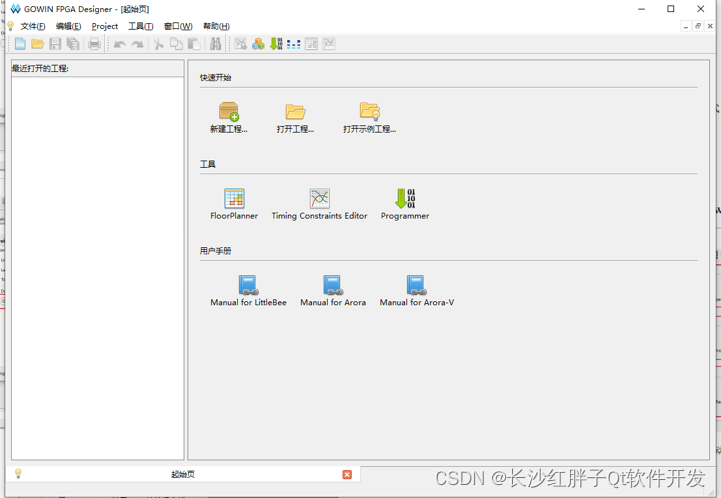

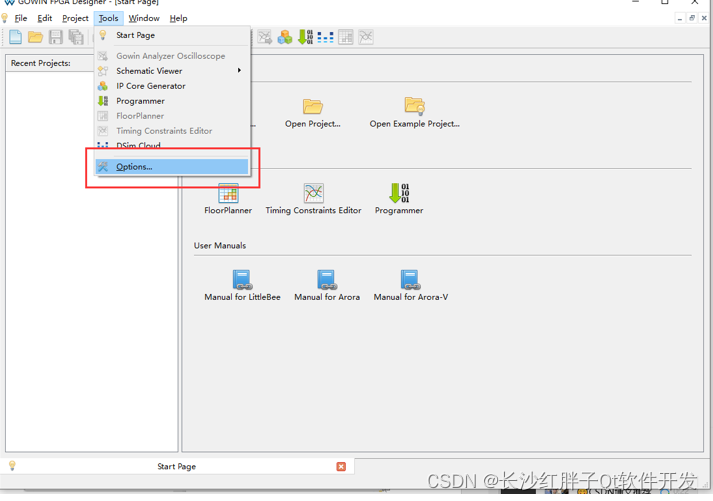

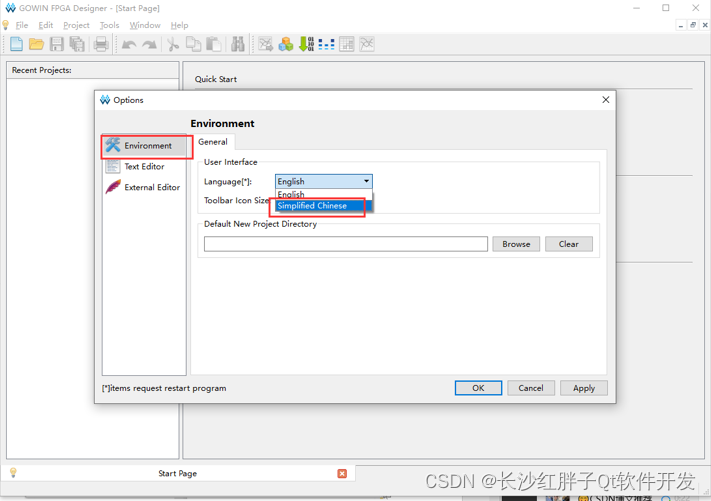

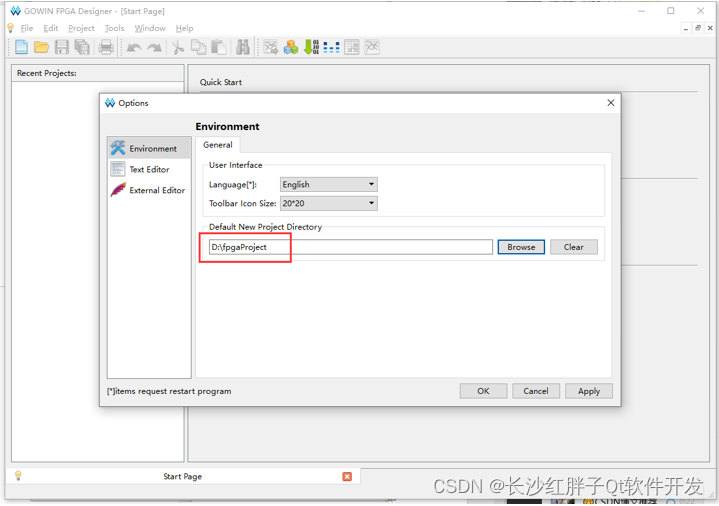

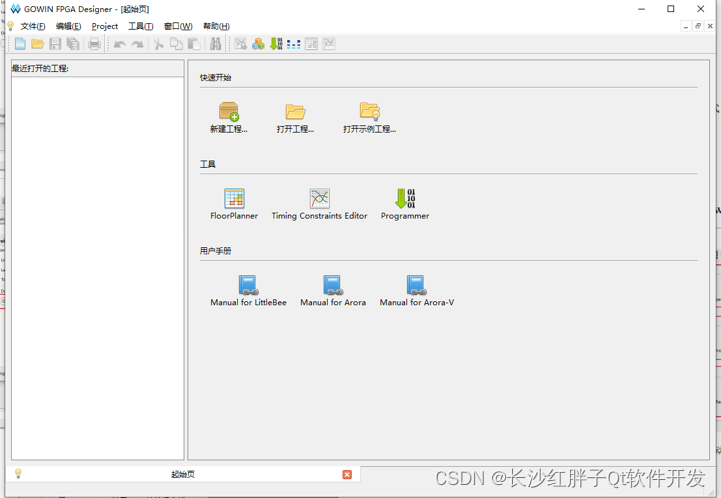

Configure the default path for Chinese and new projects

Fpga Development Process

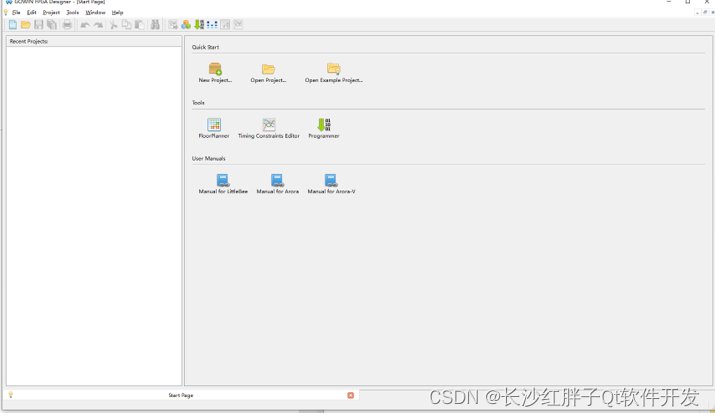

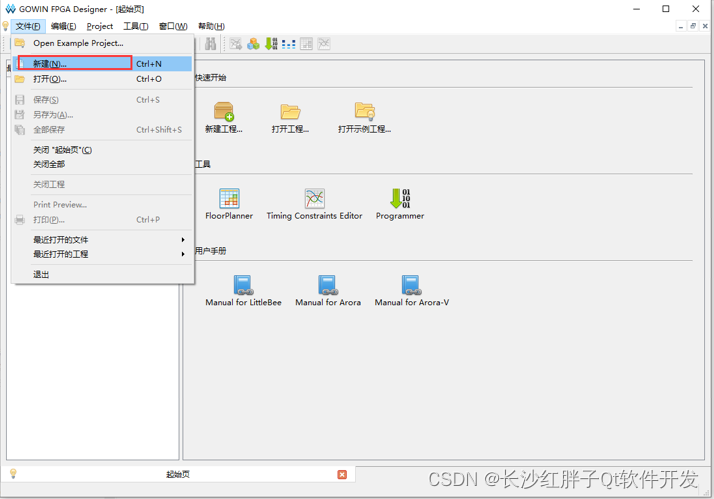

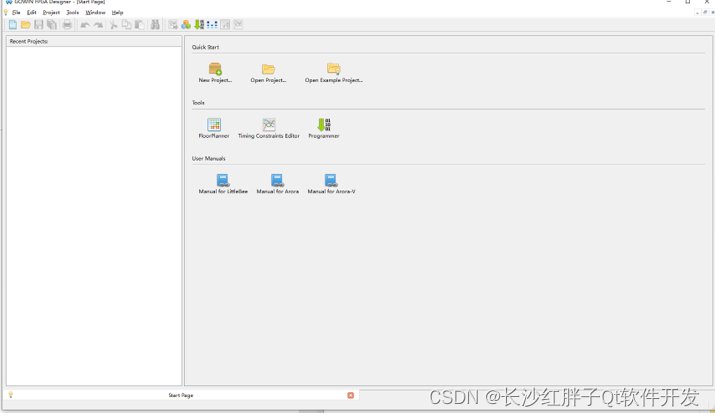

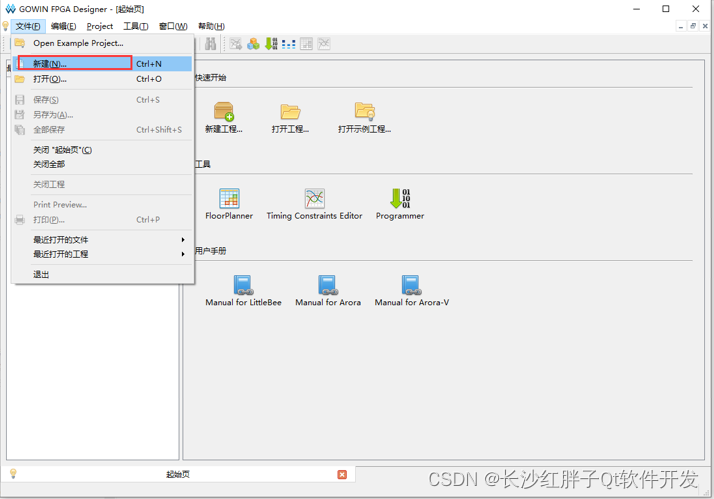

Step 1: Open the software

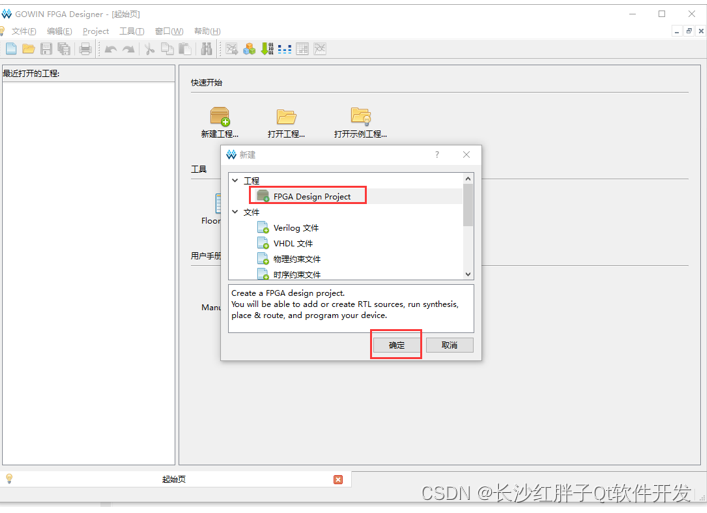

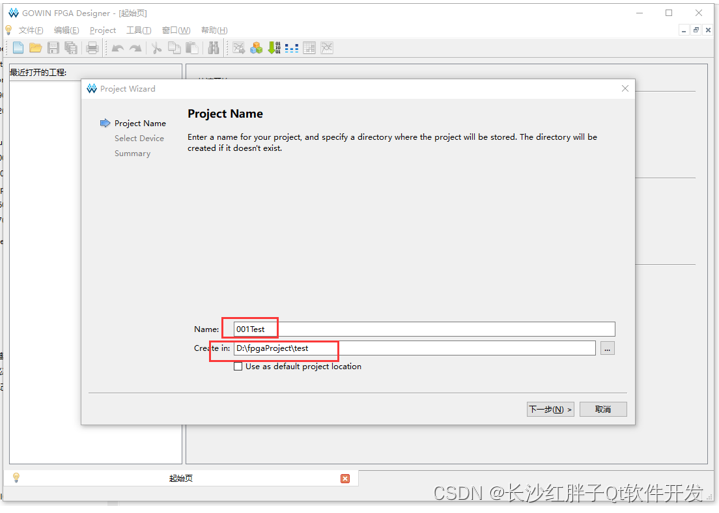

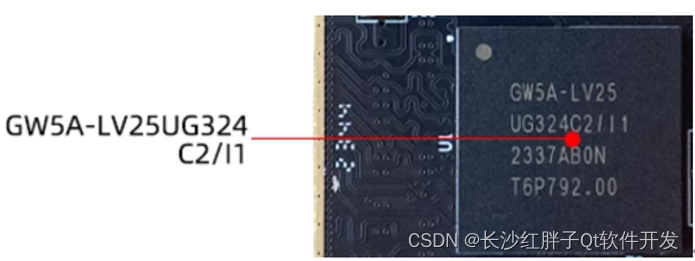

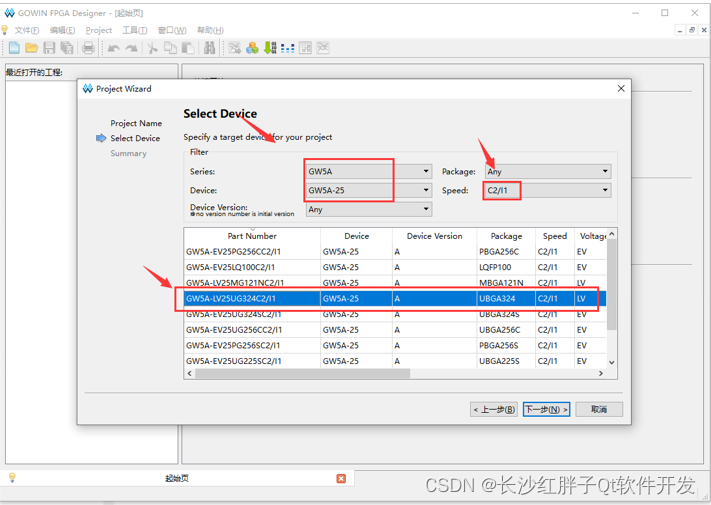

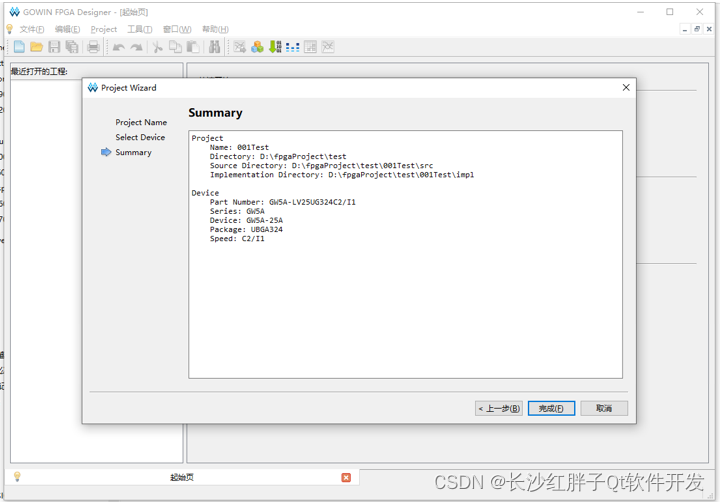

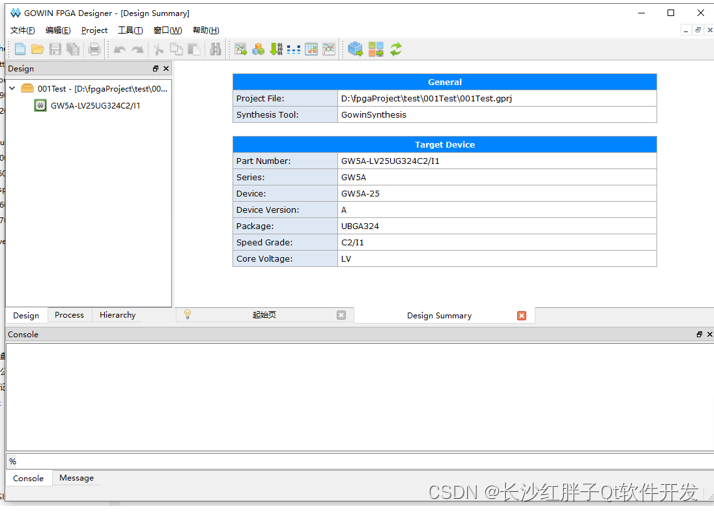

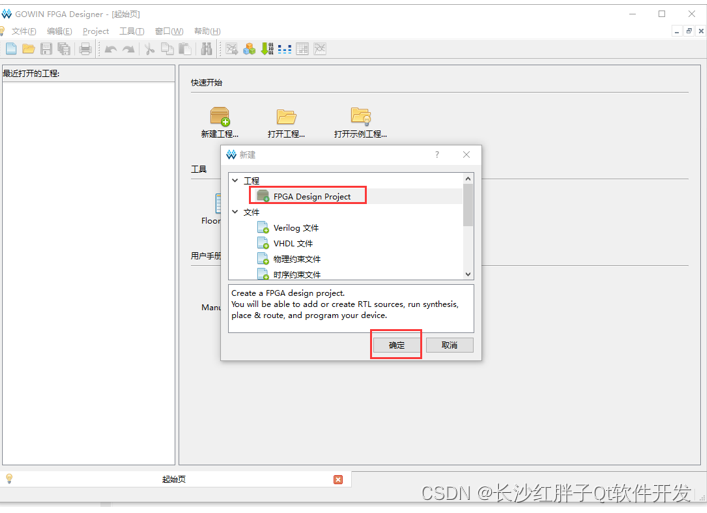

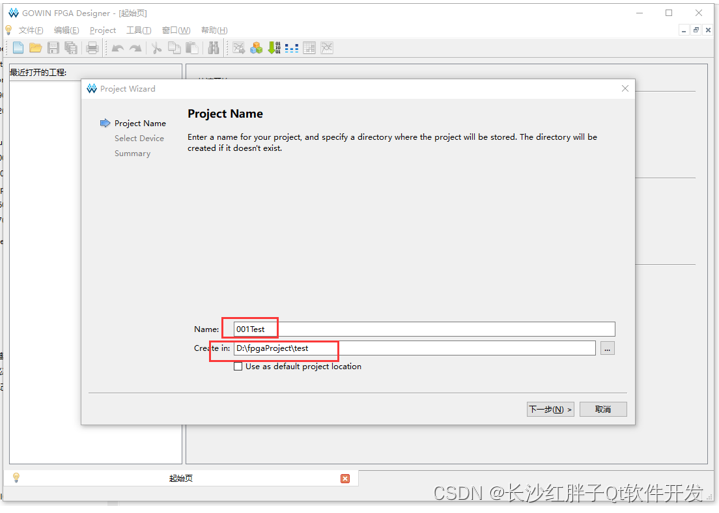

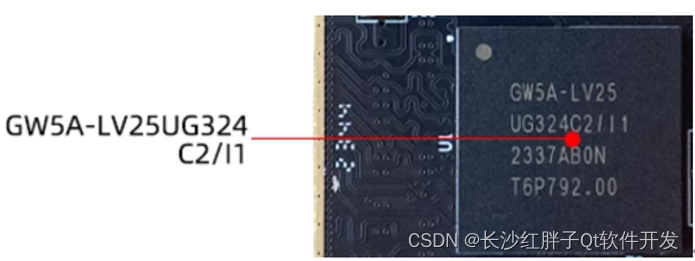

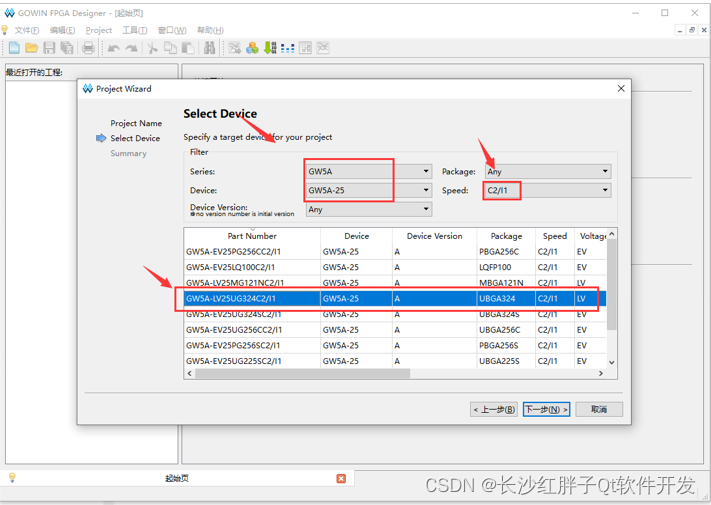

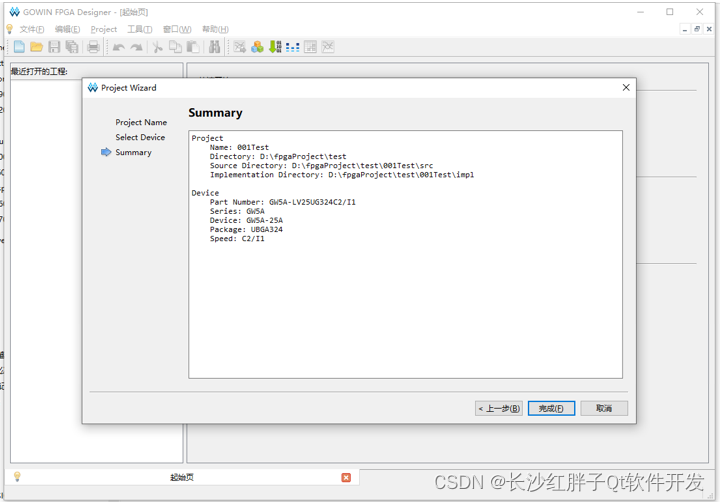

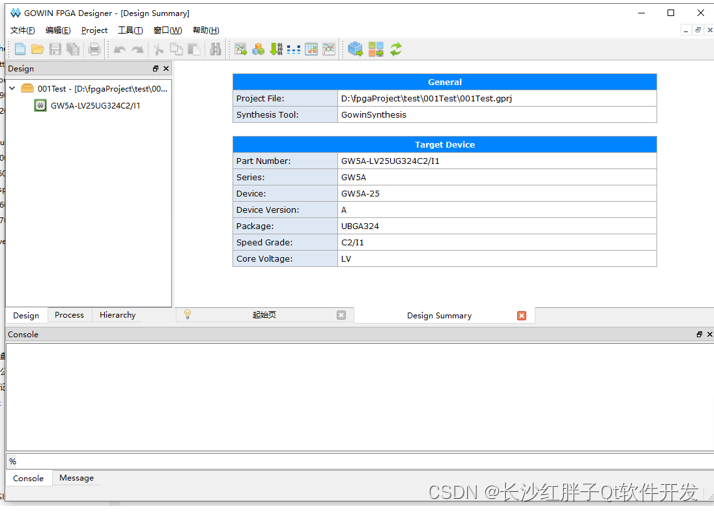

Step 2: Create Project/Open Project

Step 3: Edit/add verilog source files

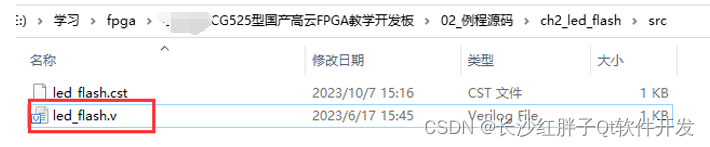

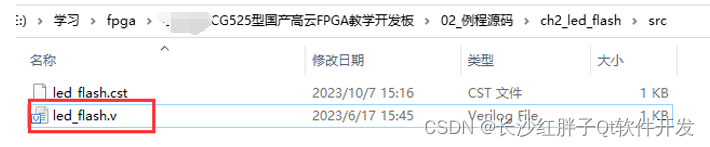

Add a verilog program source code here, take a random one from inside the demo (this is a demo program source code for inverted led light):

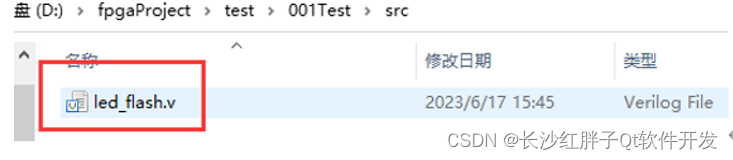

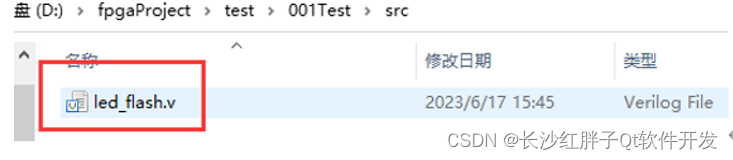

Copy it to the project under src:

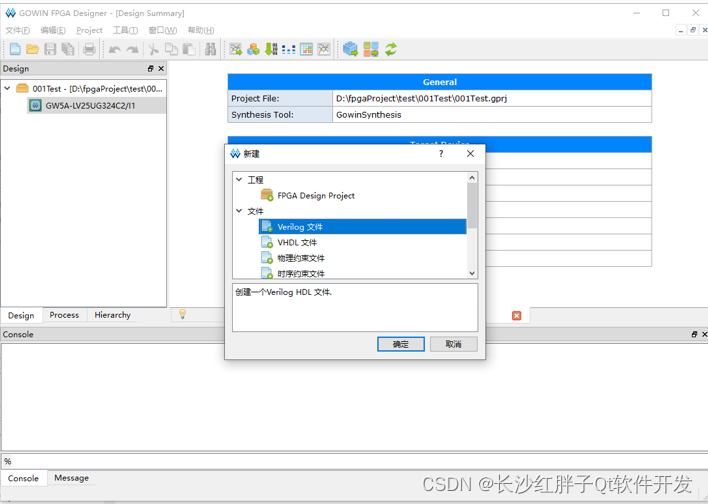

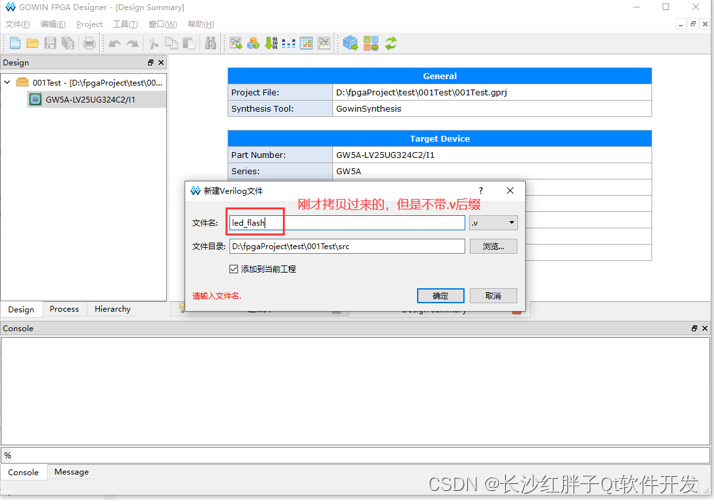

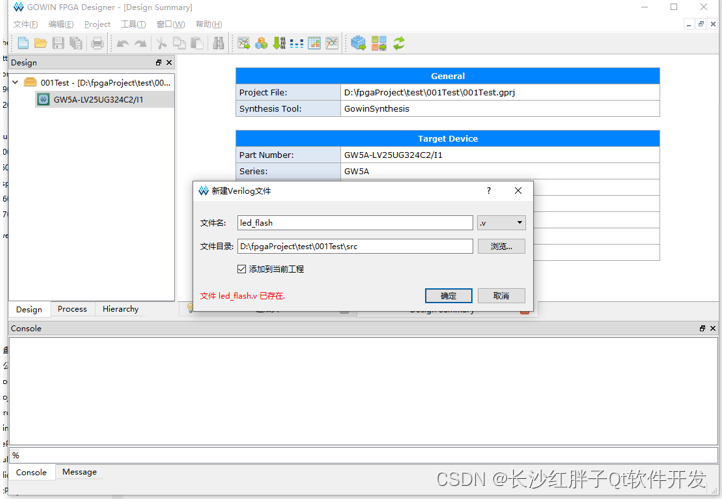

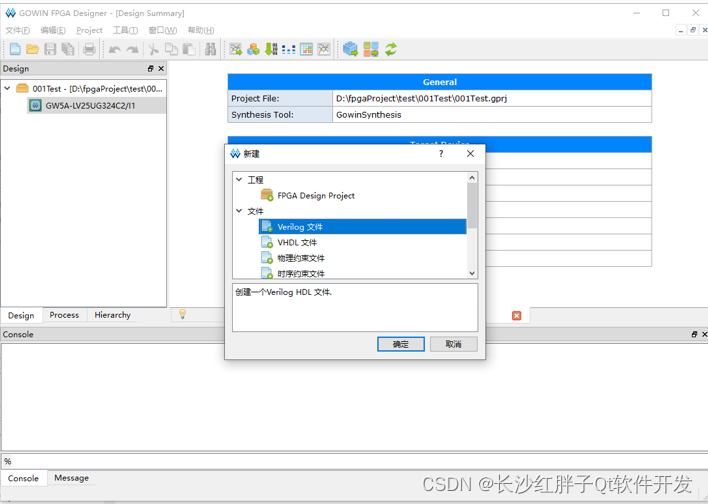

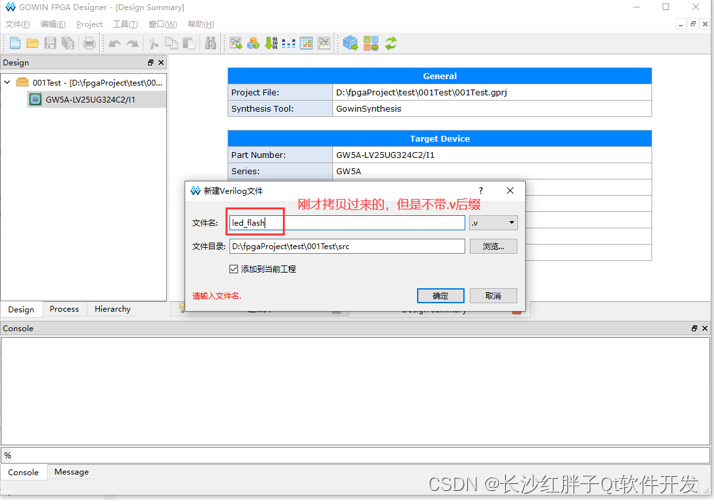

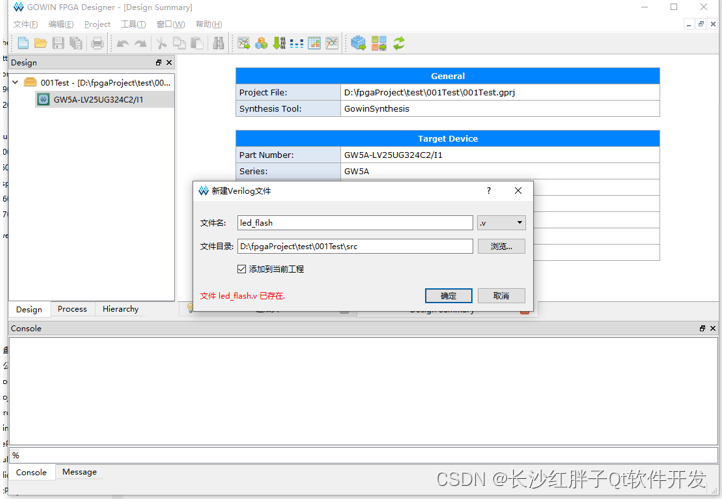

Then add the next verilog file:

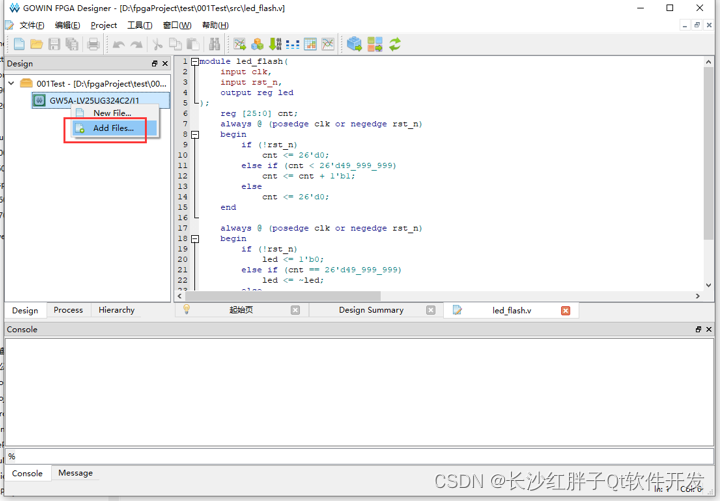

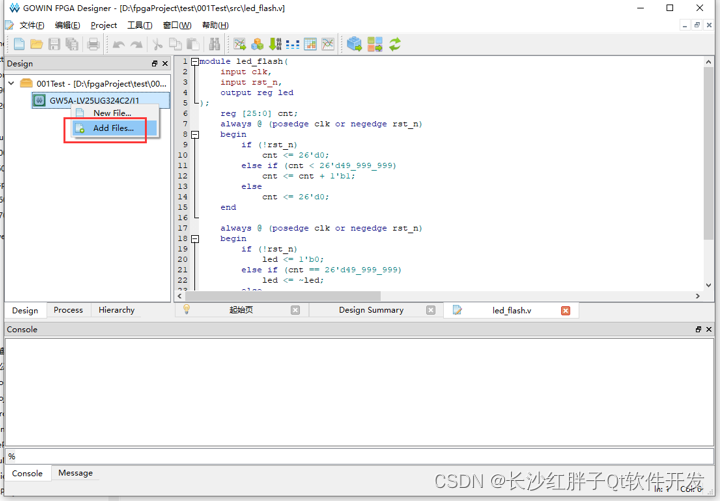

Above is the way to create a new file and below is the way to add an existing file:

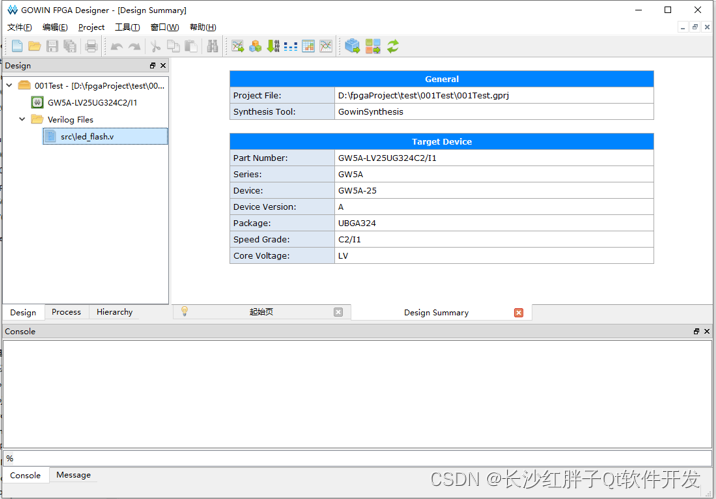

Select the .v file in the src directory:

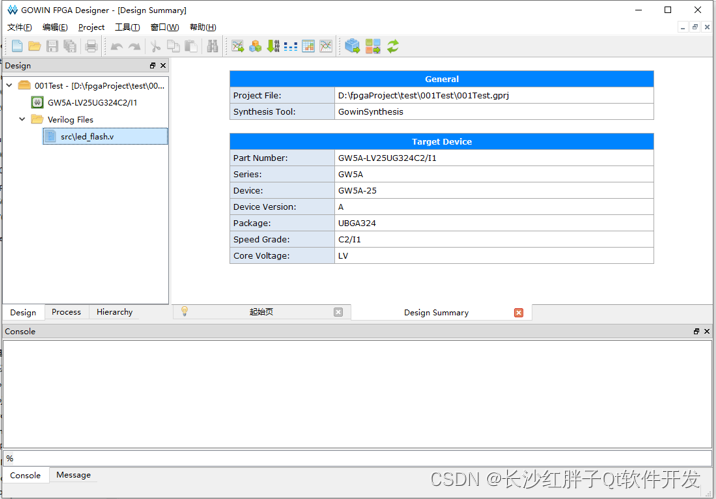

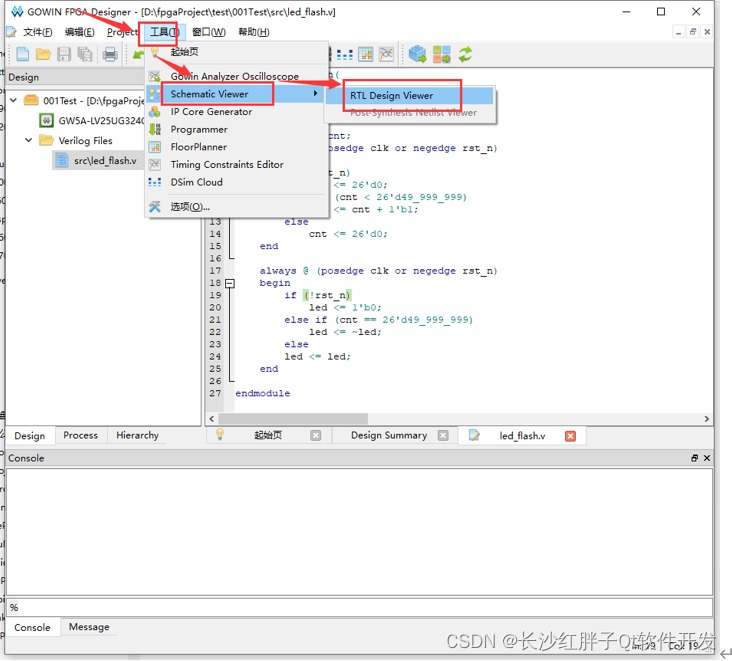

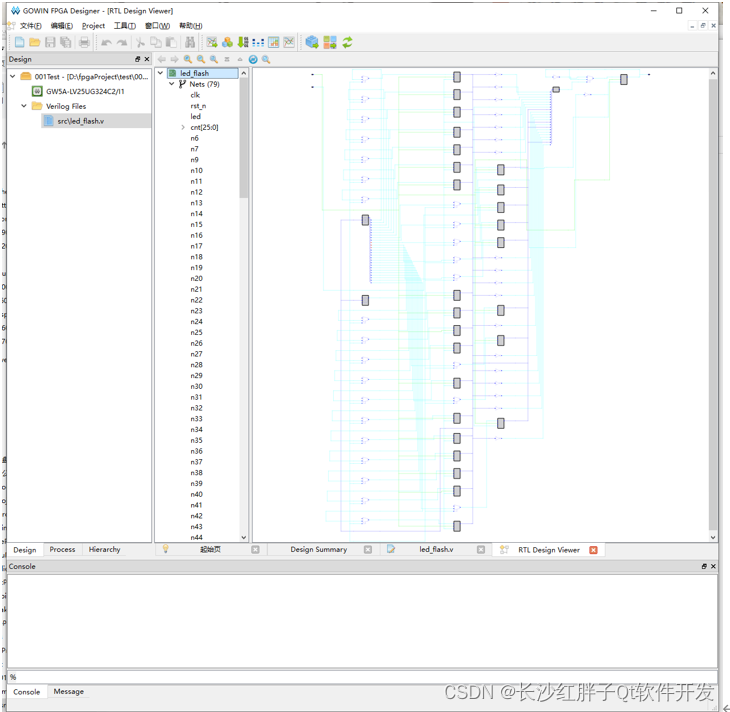

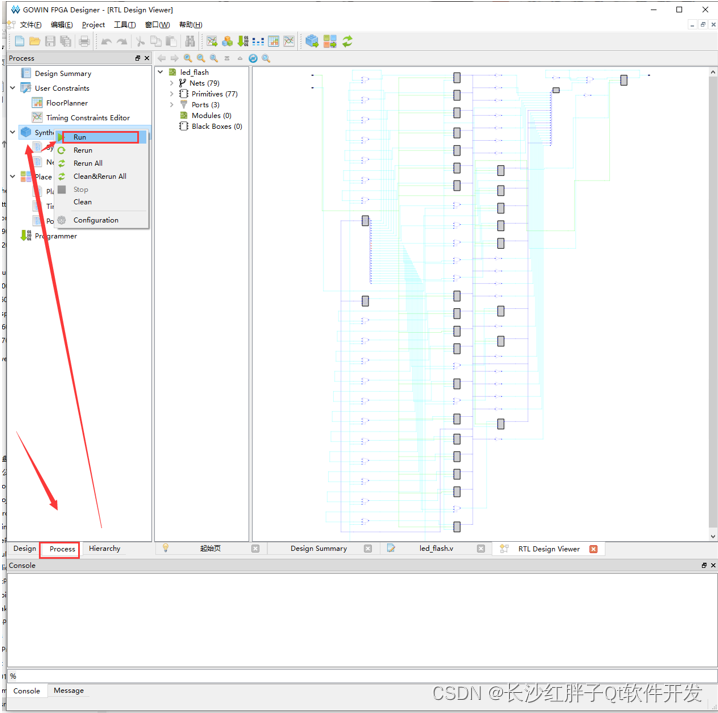

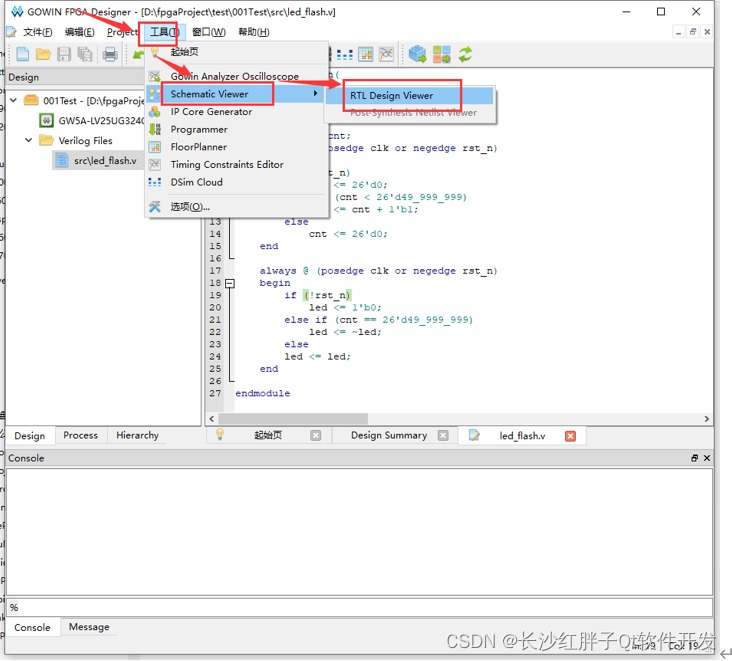

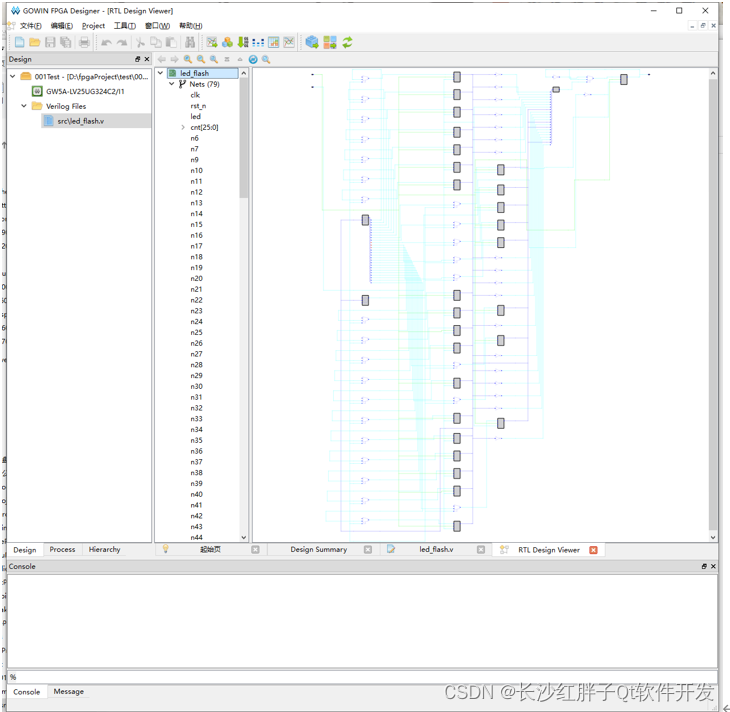

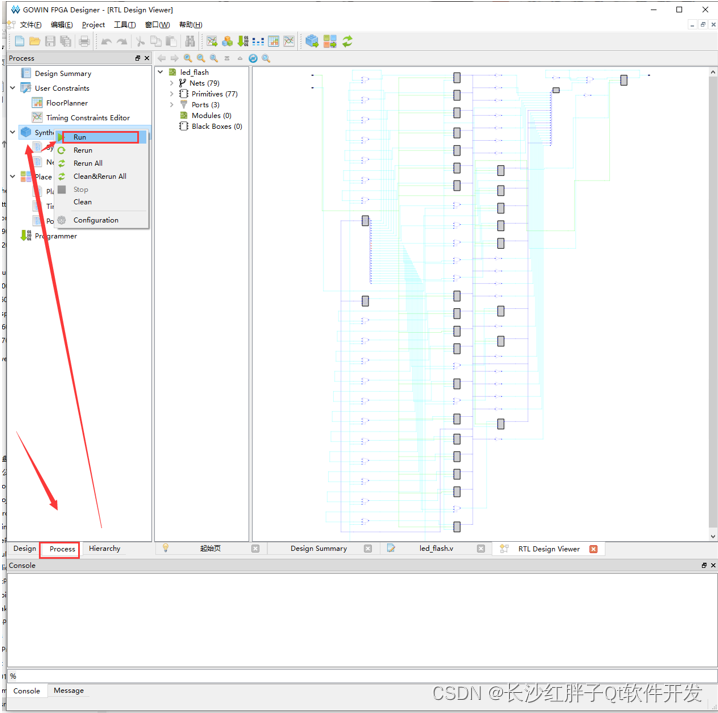

Step 4: RTL syntax analysis (equivalent to compilation for code programming)

Click on it:

Then the analysis and synthesis begins:

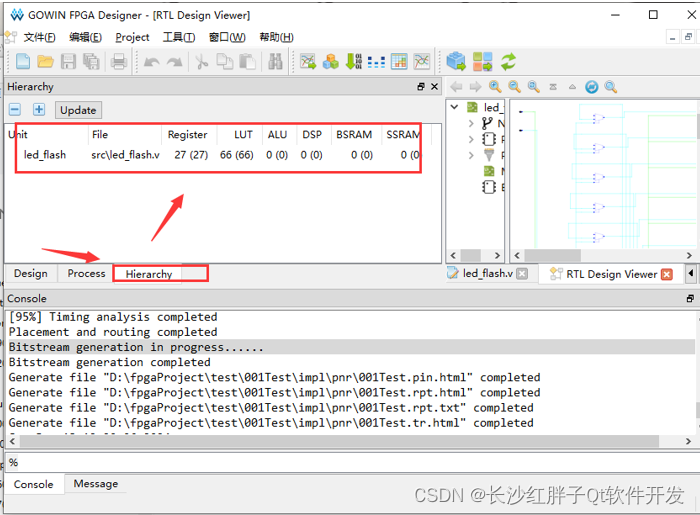

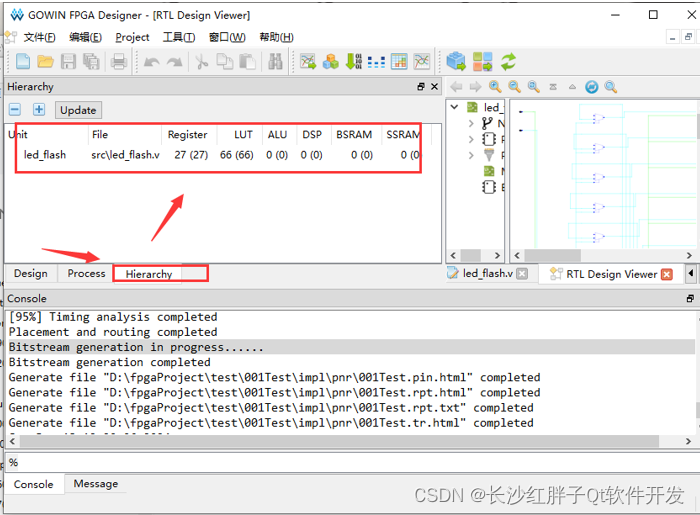

Once completed, this is the generation of the fpga’s underlying resource circuit netlist:

When finished, Hierarchy displays the resources used by the module:

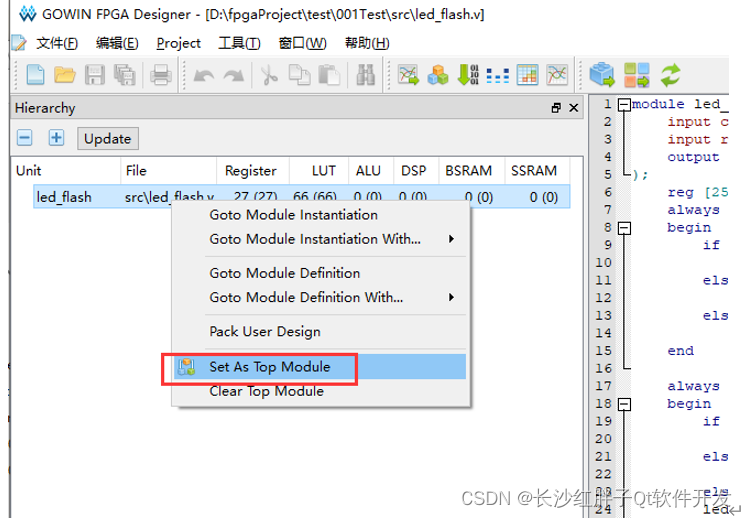

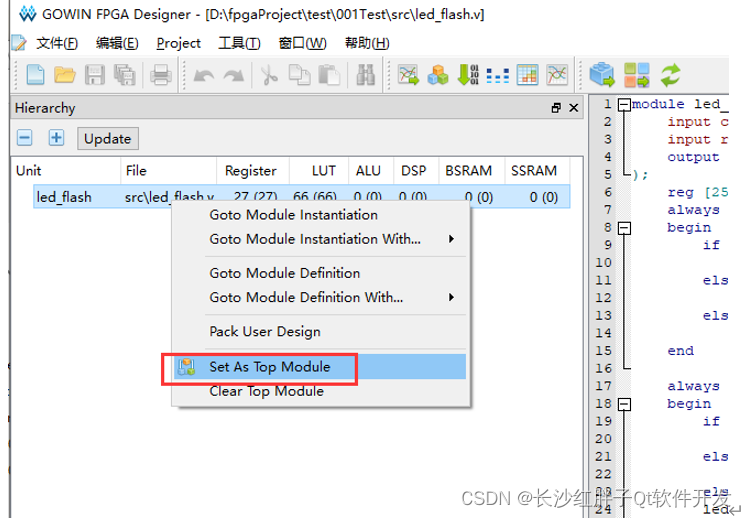

Set the top-level file:

Which program does this one seem to run.

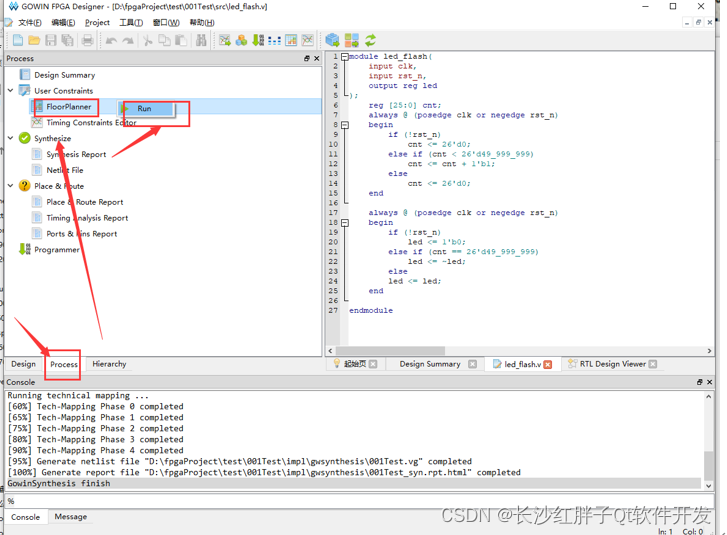

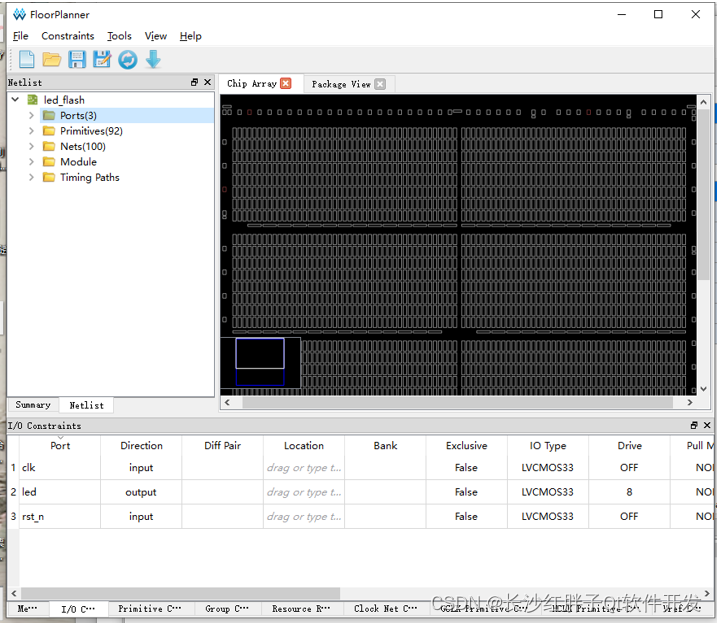

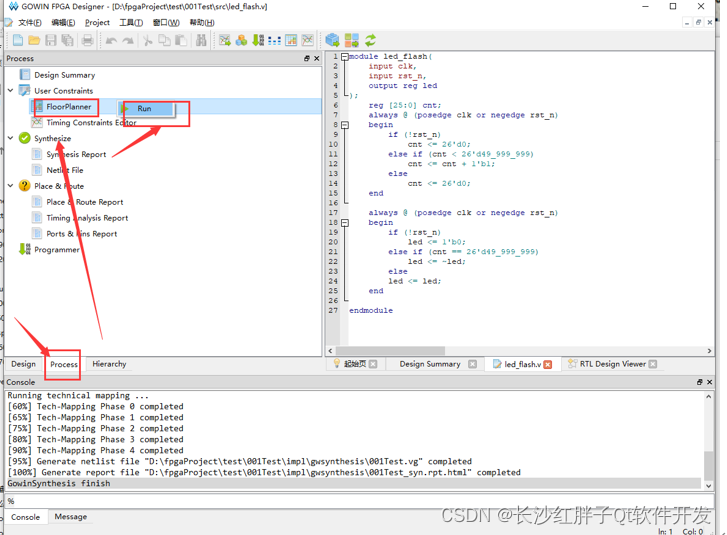

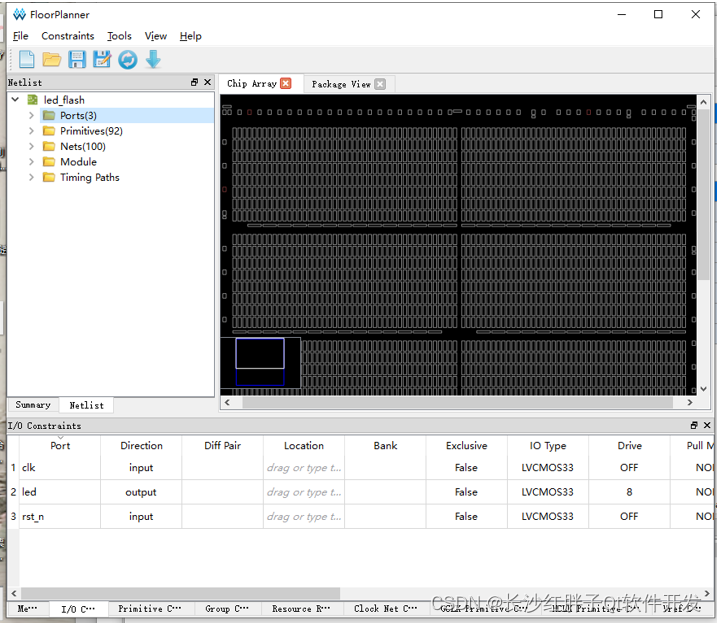

Step 5: Physical constraints

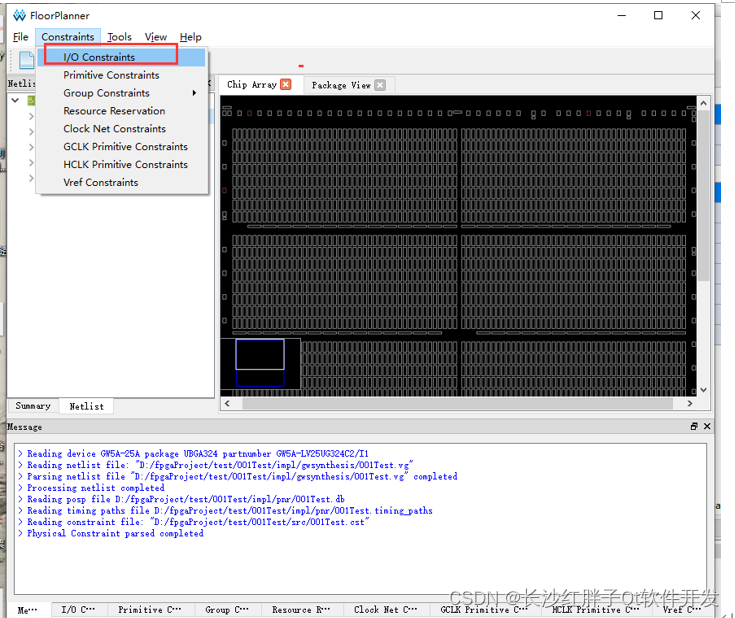

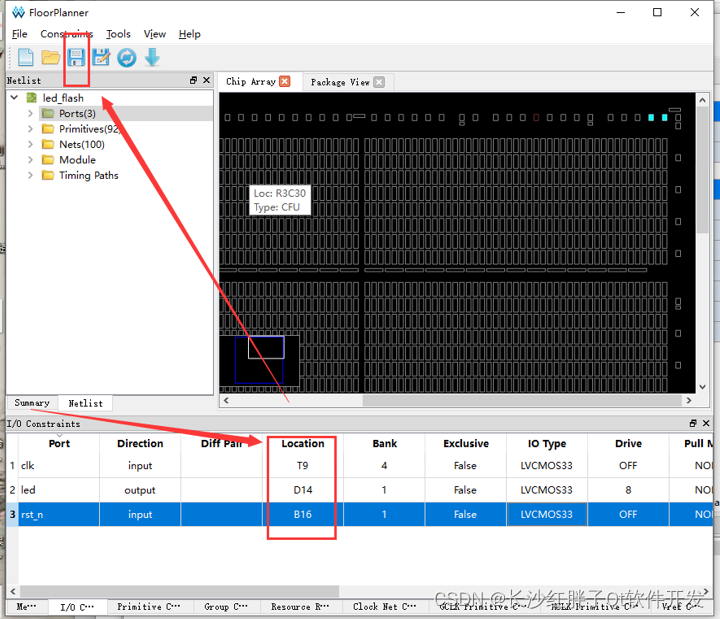

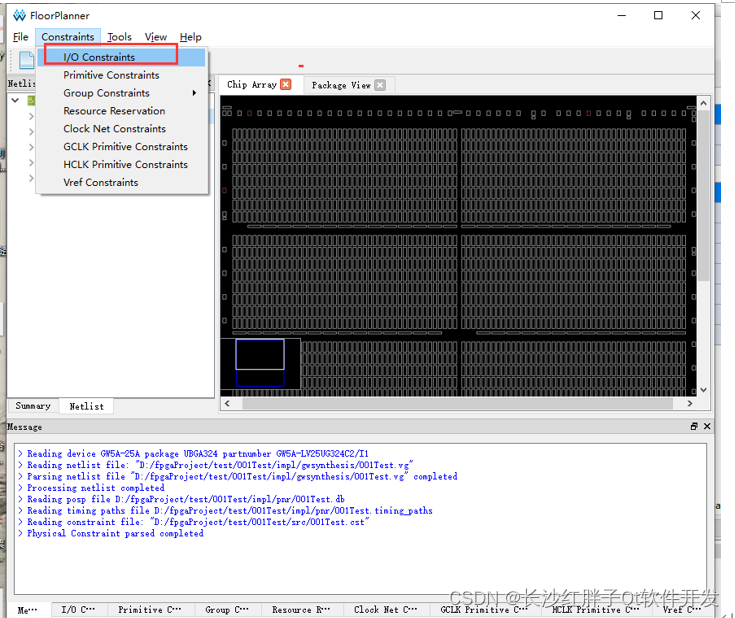

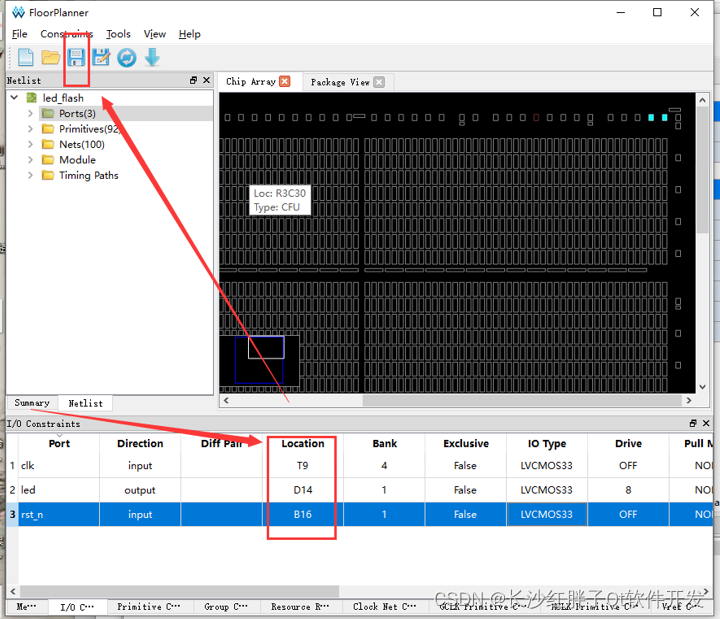

Go to the FloorPlanner interface and click I/O Constraints for I/O constraints, then assign pins and level standards according to your board.

A new box pops up:

Click on I/O Constraints:

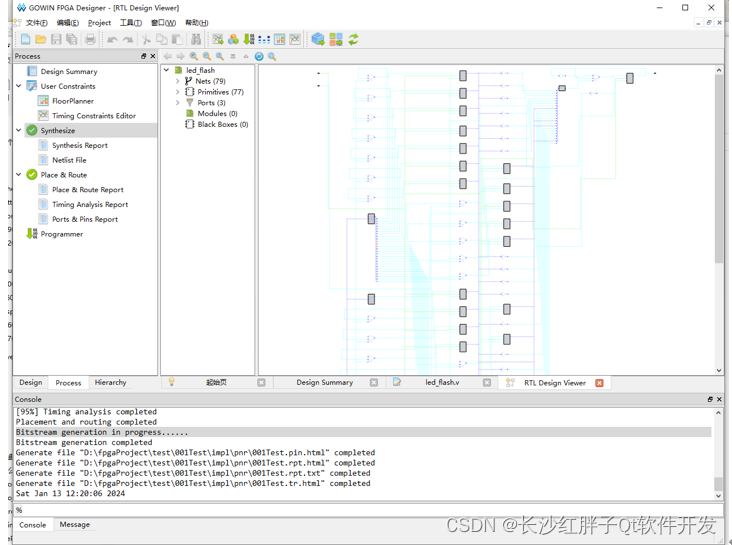

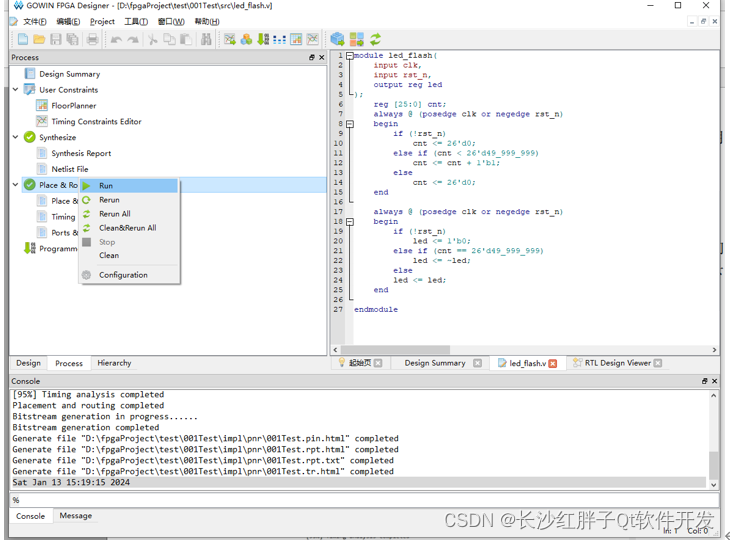

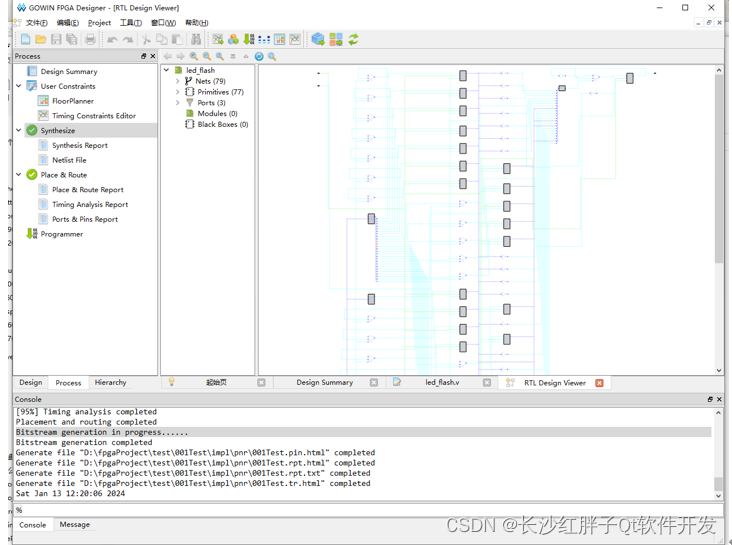

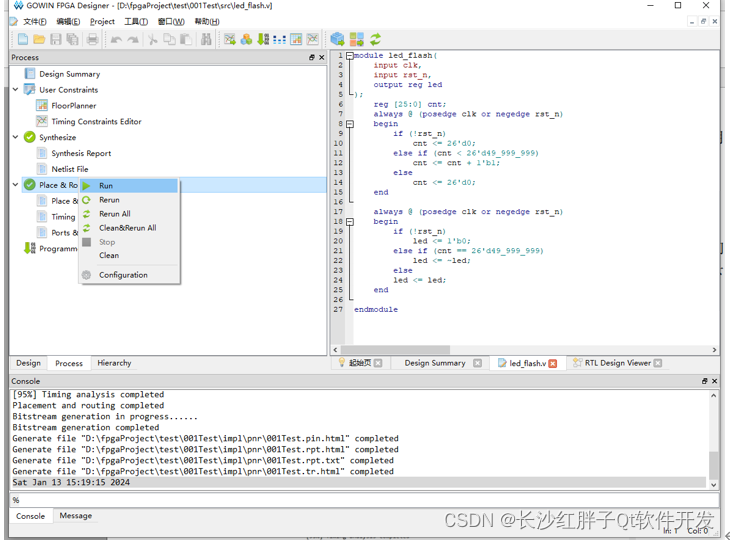

Step 6: Layout wiring

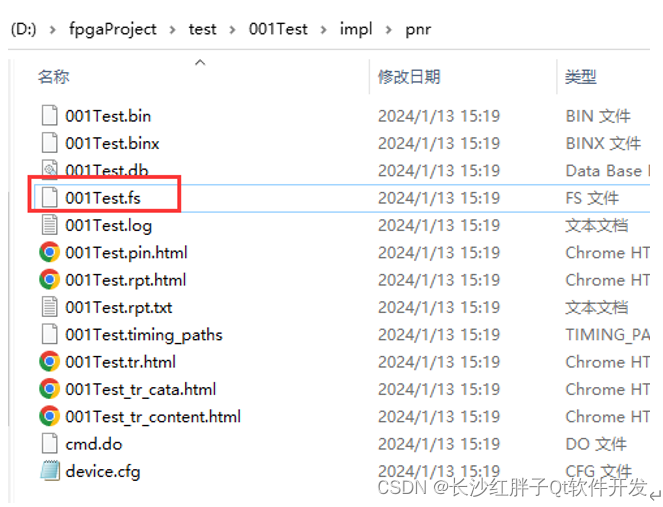

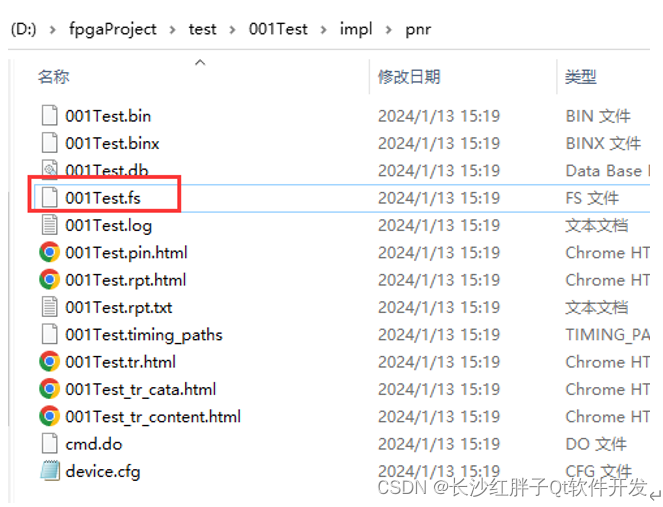

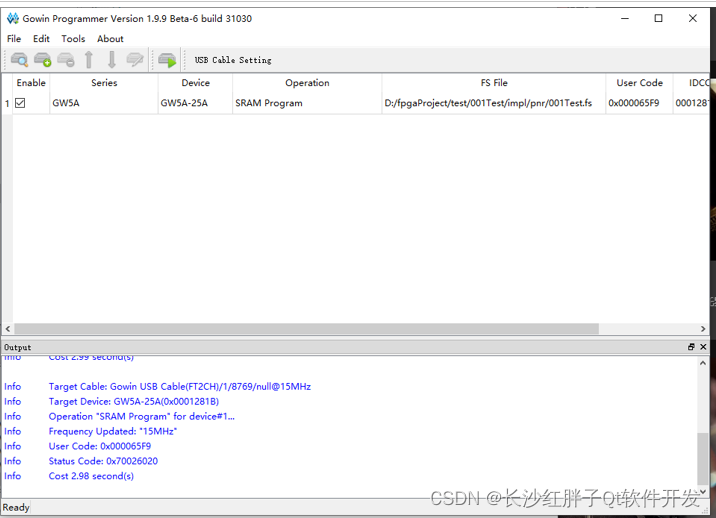

By clicking Process->Place&Route for layout and routing, if the layout and routing is successful, you will see “Bitstream generation completed”, which means that the fs file has been generated successfully, as follows:

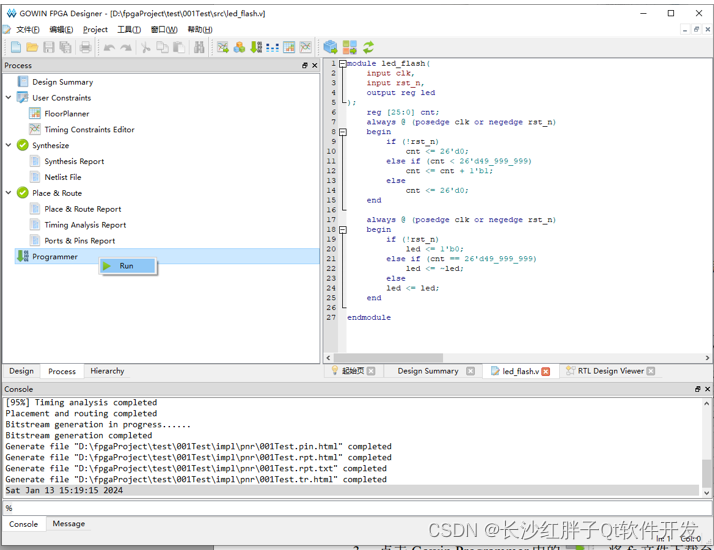

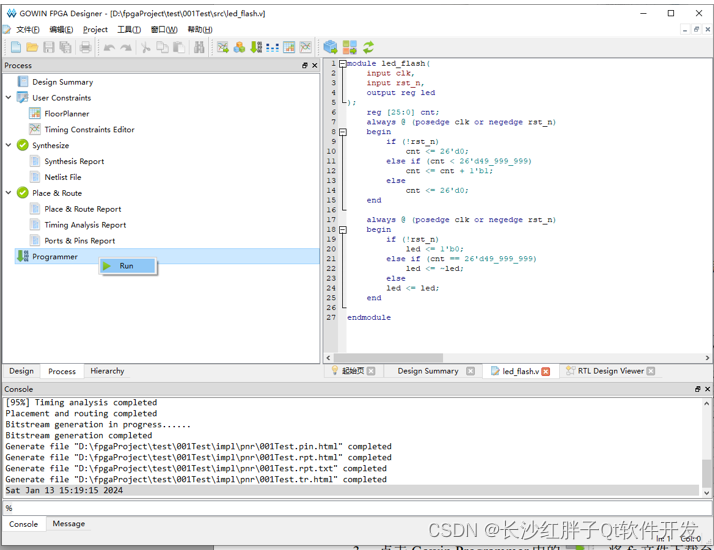

Step 7: Board-level verification (equivalent to microcontroller in-circuit debugging)

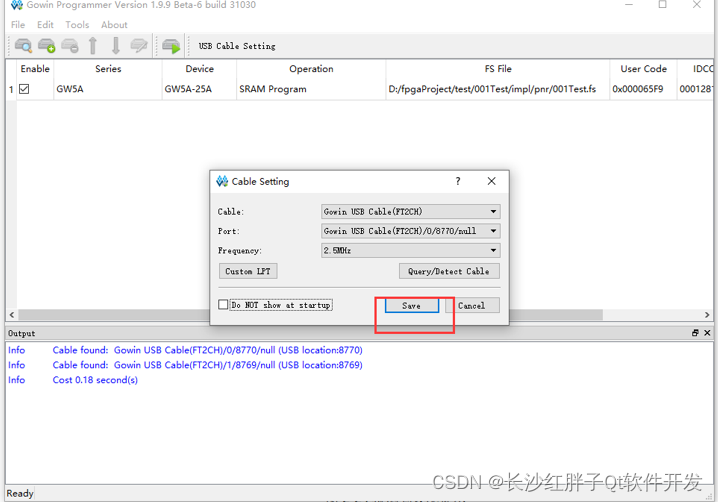

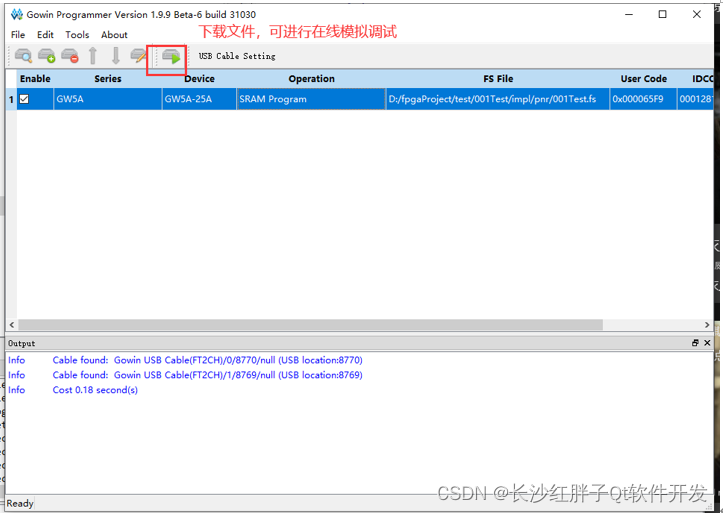

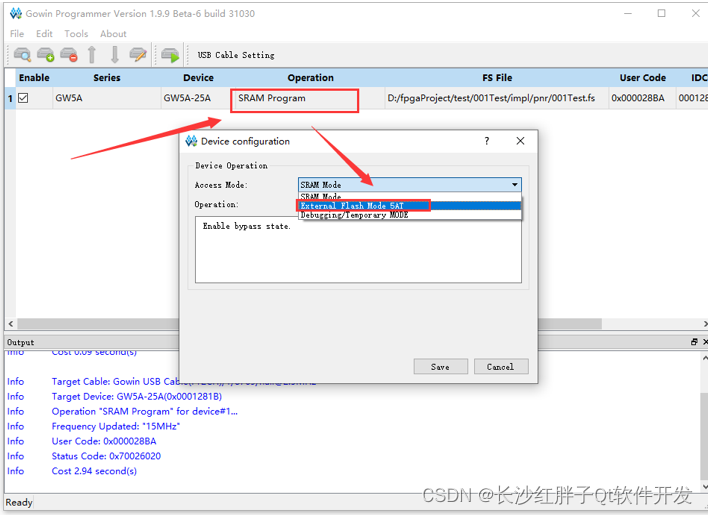

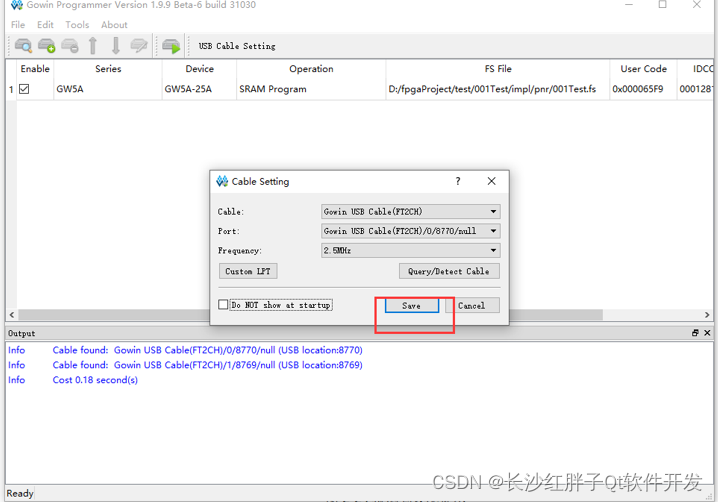

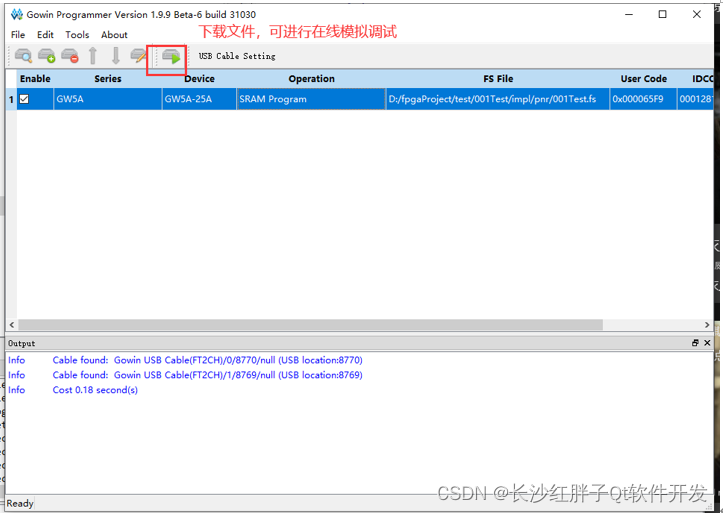

The fs file is downloaded to the FPGA chip and is used to complete the configuration of the FPGA:

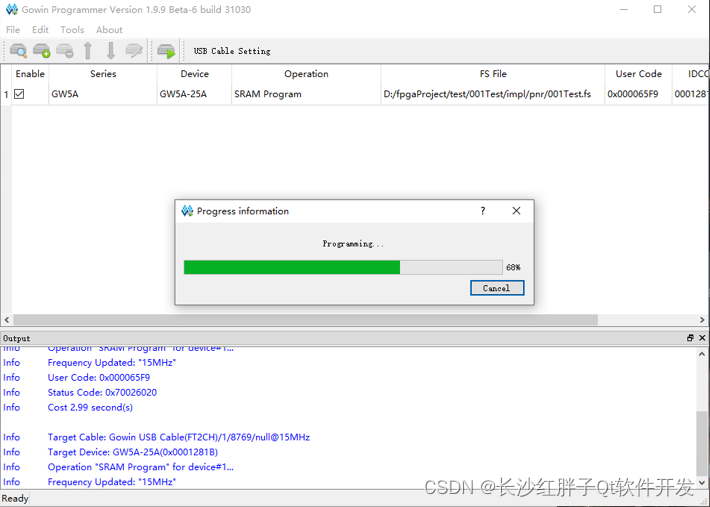

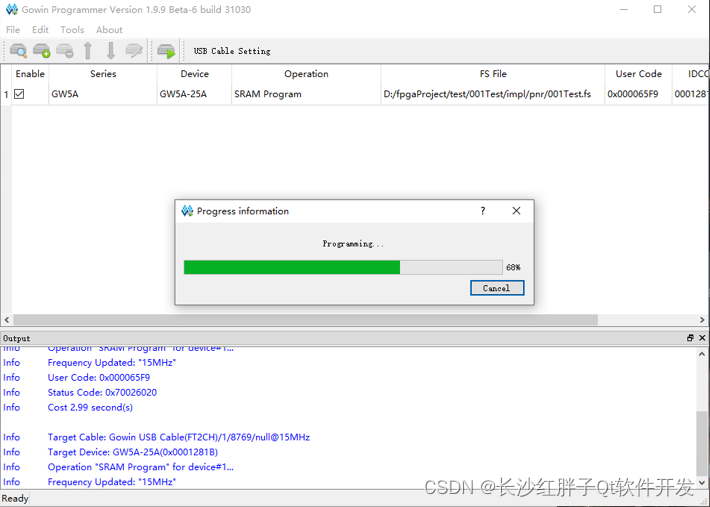

Device detected, confirming programming:

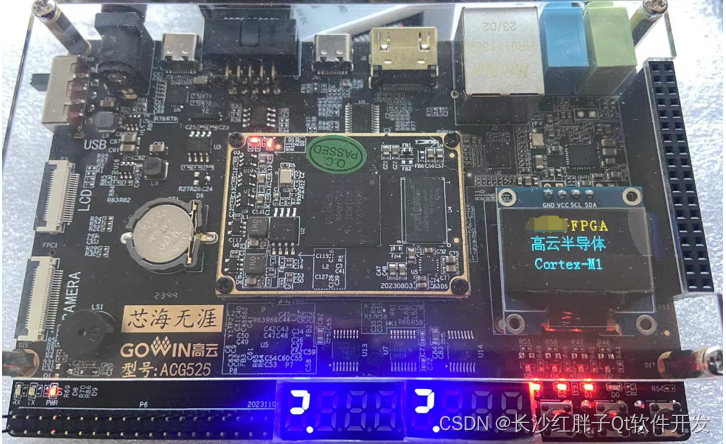

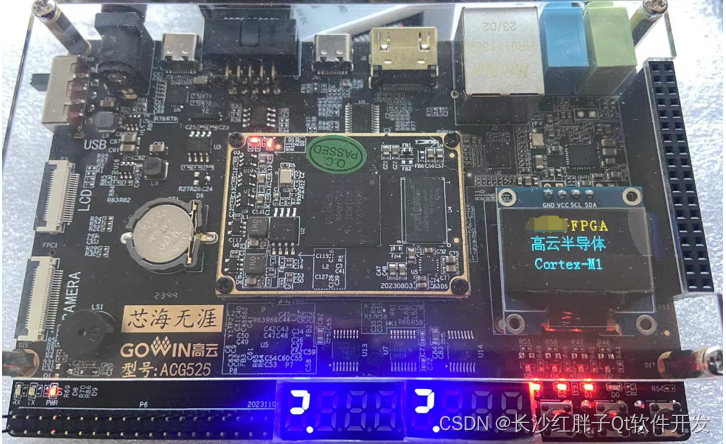

Online debugging results:

There are three lights on all the time, you can configure the lower pin output to be low (default pull-up high.):

(Here it’s down and running.)

(Note: At this time is equivalent to the microcontroller to download the program to go down the online debugging, power failure is gone, need to download brush firmware)

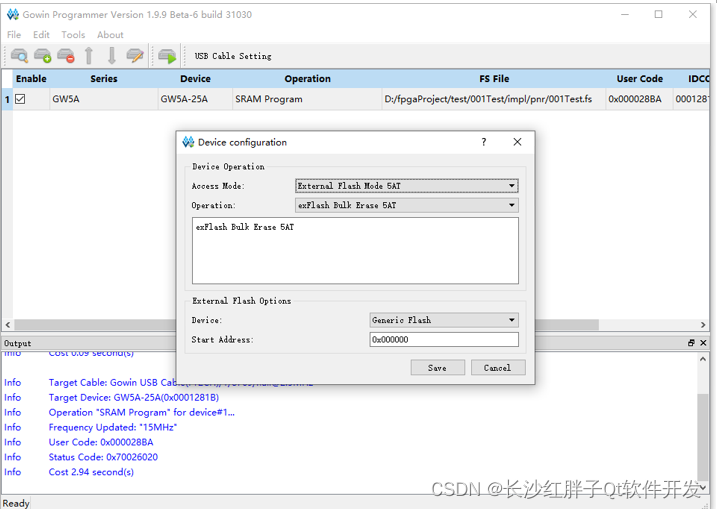

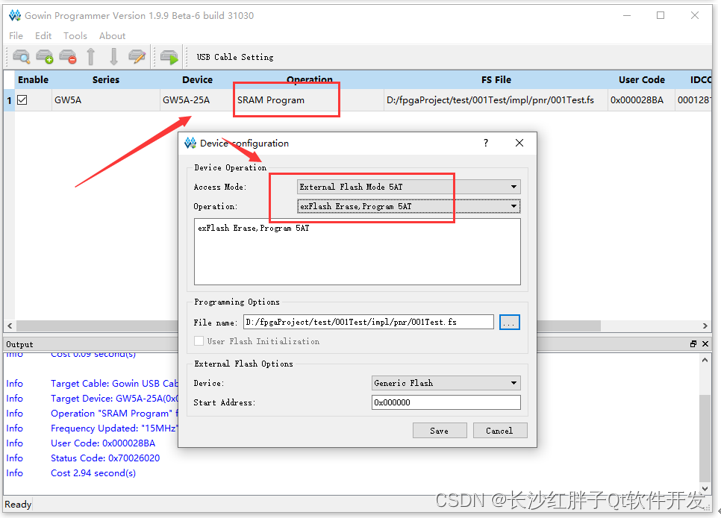

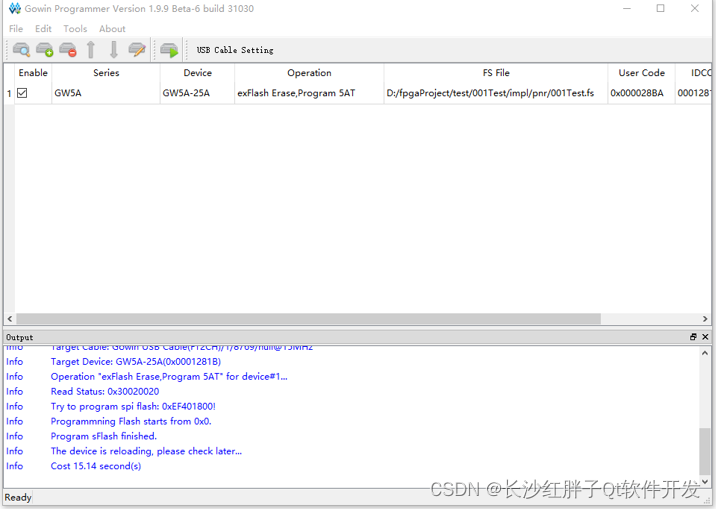

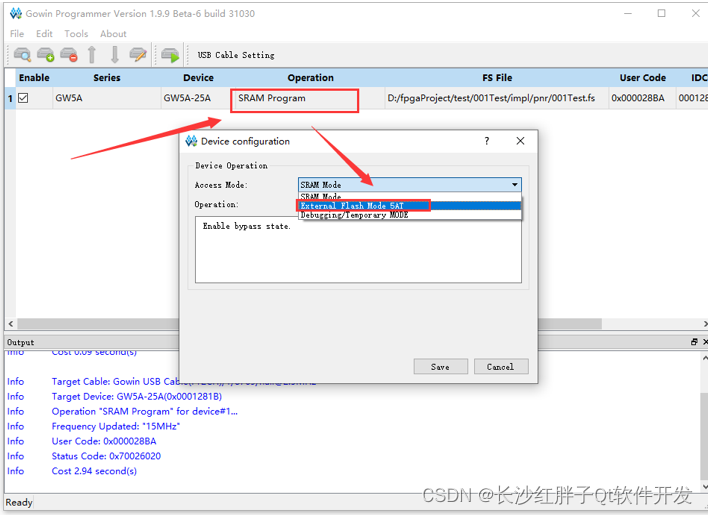

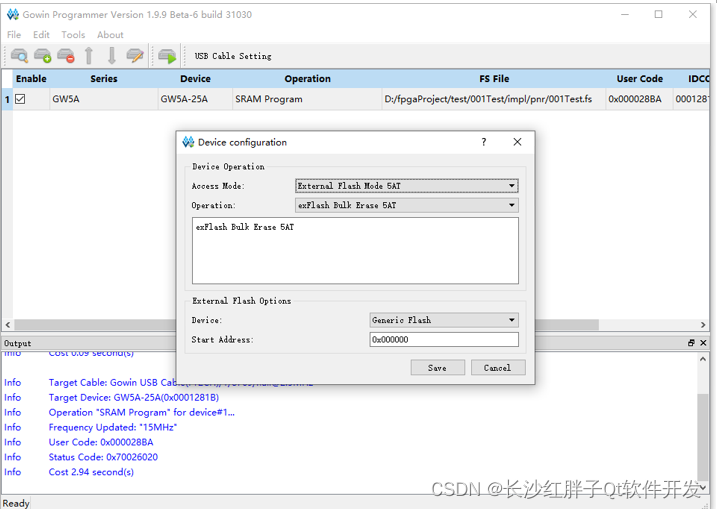

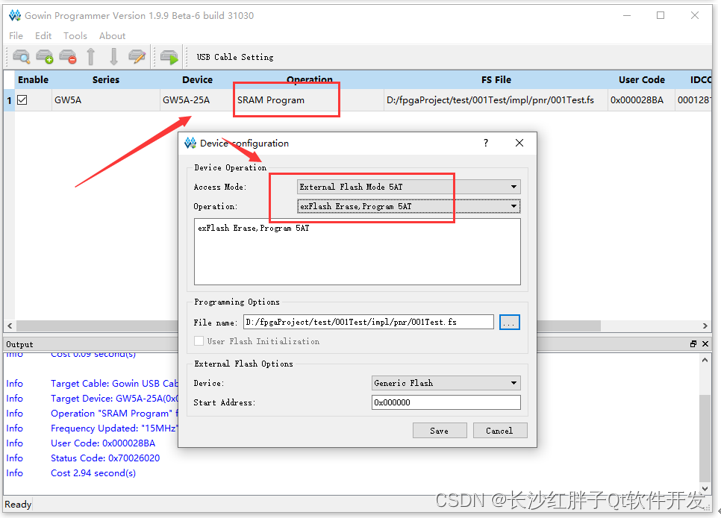

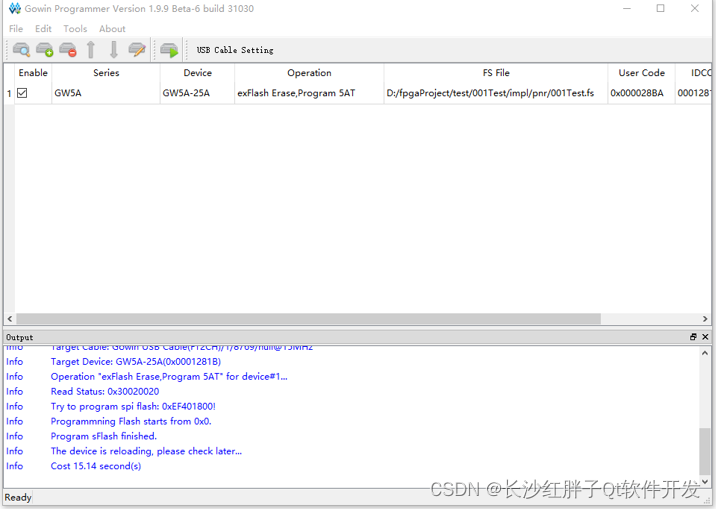

Step 8: Program curing (equivalent to downloading the degree to the microcontroller)

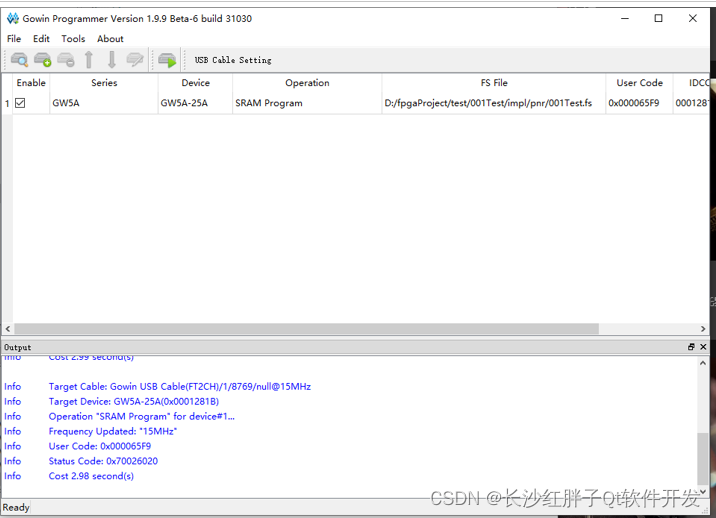

Then again, at a slower pace, the download completes:

fig. make a career out of it

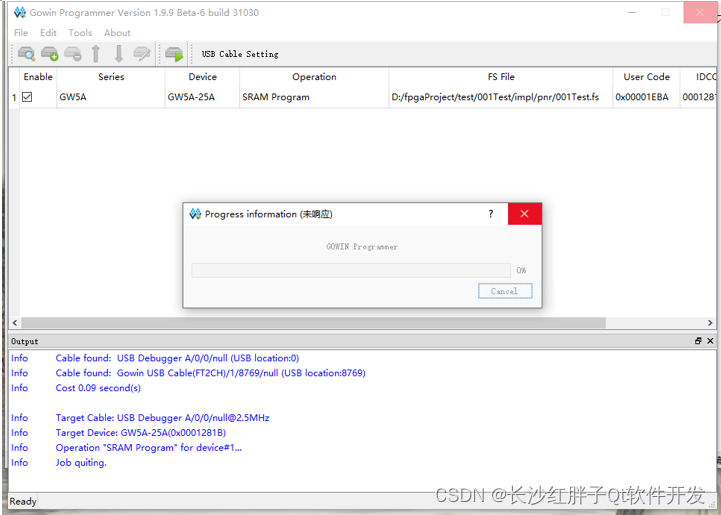

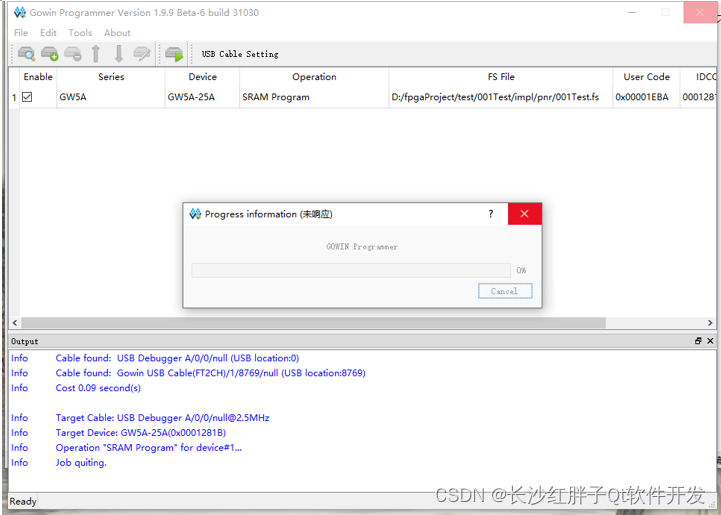

Pitfall 1: download program stuck

concern

unresponsive and stuck

rationale

currently unknown

tackle

Continue to click run can open the second window, you can download, test found that the first inevitably stuck, stuck under the premise of opening the second, the second can be downloaded, if you turn off and then open is also a, or stuck, as a bug in this download software.

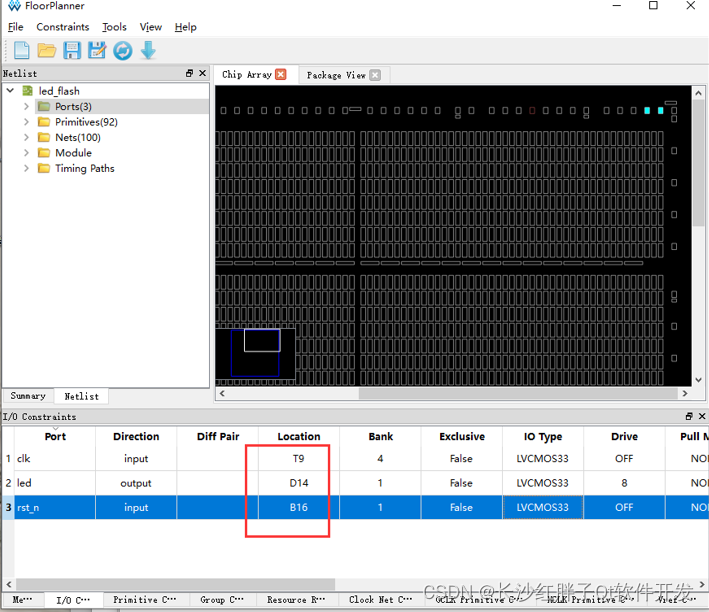

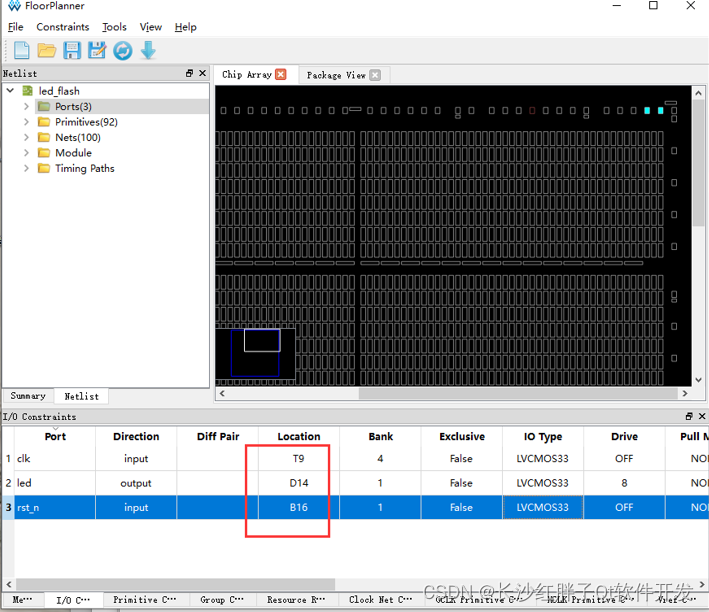

Pitfall 2: LED0 does not blink after download

concern

No blinking, all four lights on

rationale

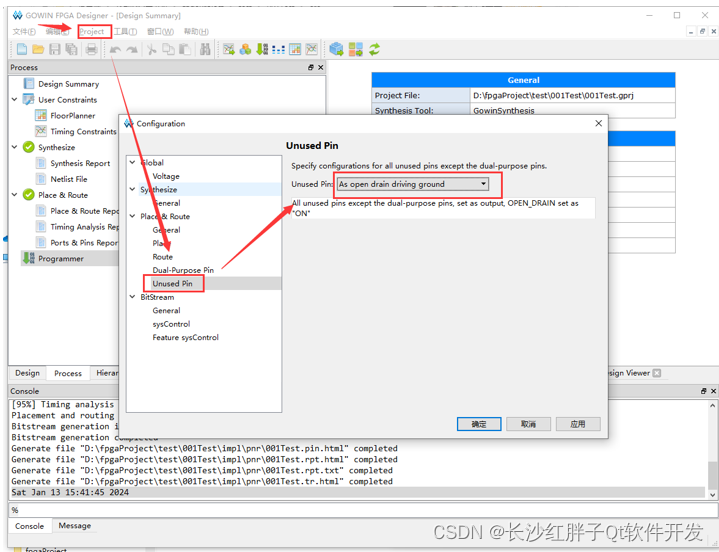

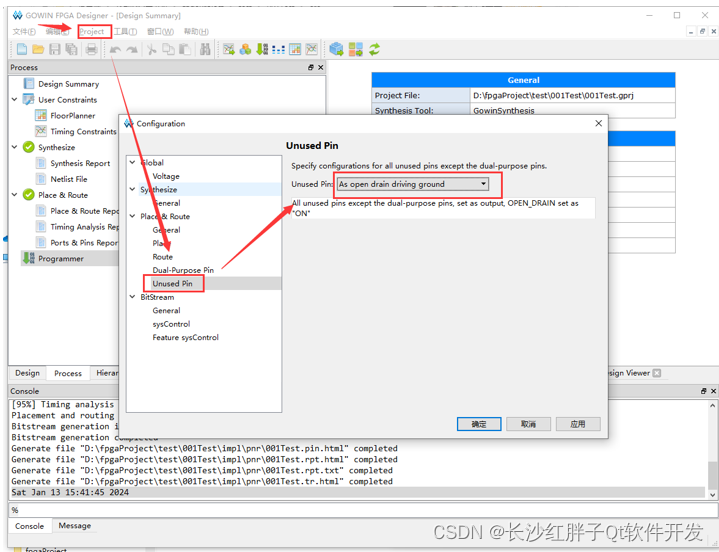

Unconstrained Pin Output

tackle

To configure the pin constraints (actually configure the pin outputs)

Previous: The

Fpga development notes (I): high-cloud FPGA chip introduction, the start of the development board kit, the core board and base board introduction》

Next articleStay tuned…

Blog address for this post:

https://hpzwl.blog.csdn.net/article/details/135620590

There is also a harmonious way this process can be viewed:

http://www.corecourse.cn/forum.php?mod=viewthread&tid=29510

After downloading the software and getting the license it is time to install the software.

There is also a harmonious way this process can be viewed:

http://www.corecourse.cn/forum.php?mod=viewthread&tid=29510

After downloading the software and getting the license it is time to install the software.

Then, there was no more then, it was straight up gone, it was the installation that was done.

Then, there was no more then, it was straight up gone, it was the installation that was done.

Drag it out and place it on the Start screen:

Drag it out and place it on the Start screen:

Click to open:

Click to open:

Above is the registration license failed or unregistered, go back and continue to register.

Above is the registration license failed or unregistered, go back and continue to register.

Copy it to the project under src:

Copy it to the project under src:

Then add the next verilog file:

Then add the next verilog file:

Above is the way to create a new file and below is the way to add an existing file:

Above is the way to create a new file and below is the way to add an existing file:

Select the .v file in the src directory:

Select the .v file in the src directory:

Click on it:

Click on it:

Then the analysis and synthesis begins:

Then the analysis and synthesis begins:

Once completed, this is the generation of the fpga’s underlying resource circuit netlist:

Once completed, this is the generation of the fpga’s underlying resource circuit netlist:

When finished, Hierarchy displays the resources used by the module:

When finished, Hierarchy displays the resources used by the module:

Set the top-level file:

Set the top-level file:

Which program does this one seem to run.

Which program does this one seem to run.

A new box pops up:

A new box pops up:

Click on I/O Constraints:

Click on I/O Constraints:

Device detected, confirming programming:

Device detected, confirming programming:

Online debugging results:

Online debugging results:

There are three lights on all the time, you can configure the lower pin output to be low (default pull-up high.):

There are three lights on all the time, you can configure the lower pin output to be low (default pull-up high.):

(Here it’s down and running.)

(Here it’s down and running.)

(Note: At this time is equivalent to the microcontroller to download the program to go down the online debugging, power failure is gone, need to download brush firmware)

Step 8: Program curing (equivalent to downloading the degree to the microcontroller)

(Note: At this time is equivalent to the microcontroller to download the program to go down the online debugging, power failure is gone, need to download brush firmware)

Step 8: Program curing (equivalent to downloading the degree to the microcontroller)

Then again, at a slower pace, the download completes:

Then again, at a slower pace, the download completes:

Previous: TheFpga development notes (I): high-cloud FPGA chip introduction, the start of the development board kit, the core board and base board introduction》

Next articleStay tuned…

Blog address for this post:https://hpzwl.blog.csdn.net/article/details/135620590

Previous: TheFpga development notes (I): high-cloud FPGA chip introduction, the start of the development board kit, the core board and base board introduction》

Next articleStay tuned…

Blog address for this post:https://hpzwl.blog.csdn.net/article/details/135620590